bq40z50-R2 ZHCSGX4A -JUNE 2017-REVISED OCTOBER 2017

# bq40z50-R2 1 节、2 节、3 节和 4 节串联锂离子电池组管理器

## 特性

- 完全集成的 1节, 2节, 3节和 4节串联锂离子或 者锂聚合物电池组管理器和保护

- 下一代已获专利的Impedance Track™技术可准确 测量锂离子和锂聚合物电池中的可用电量

- 高侧 N 通道保护场效应晶体管 (FET) 驱动

- 充电或者静止状态时集成的电池均衡

- 适合于 100mAh 和 29Ah 之间的电池

- 全面的可编程保护 功能

- 电压

- 电流

- 温度

- 充电终止时间

- CHG/DSG FET

- 模拟前端 (AFE)

- 精密的充电算法

- 日本电子与信息技术工业协会 (JEITA)

- 增强型充电

- 自适应充电

- 电池均衡

- 支持TURBO模式 2.0

- 支持电池跳闸点 (BTP)

- 诊断使用寿命数据监控器和黑盒记录器

- 发光二极管 (LED) 显示

- 支持 2 线制系统管理总线 (SMBus) v1.1 接口

- 安全散列算法 (SHA-1) 认证

- IATA 支持

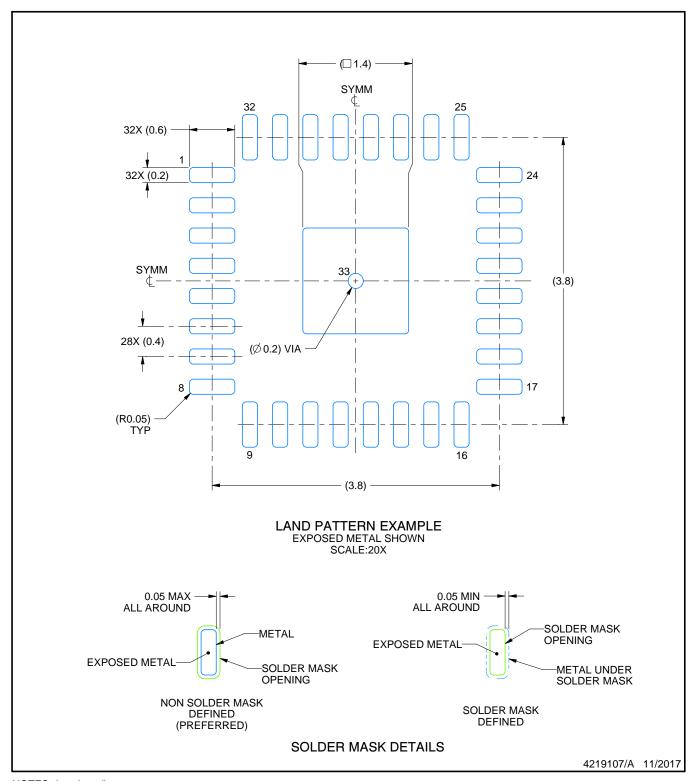

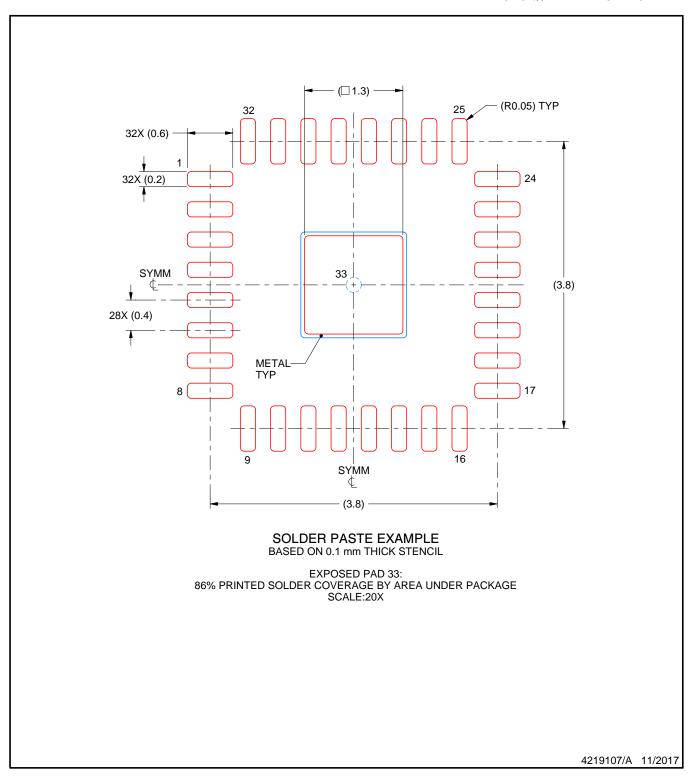

- 紧凑型封装: 32 引脚 QFN (RSM)

## 应用

- 平板电脑

- 无人机

- UPS/电池备用系统

- 医疗设备

- 手持式真空吸尘器和扫地机器人

## 3 说明

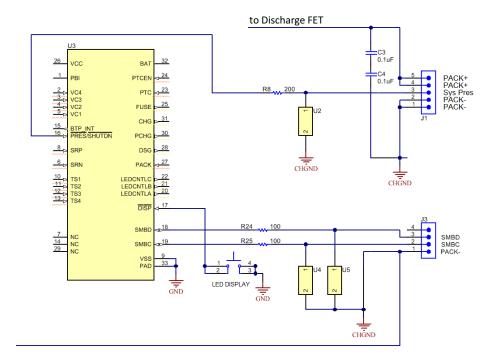

bq40z50-R2 器件采用已获专利的 阻抗跟踪™技术, 是一款基于电池组的单芯片全集成解决方案,为1 节、2 节、3 节和 4 节串联锂离子和锂聚合物电池组的 电量监测、保护及认证提供一系列丰富的 特性。

bq40z50-R2 器件利用其集成的高性能模拟外设,测量 锂离子或锂聚合物电池的可用容量、电压、电流、温度 和其他关键参数,保留准确的数据记录,并通过 SMBus v1.1 兼容接口将这些信息报告给系统主机控制

### 器件信息(1)

| 器件型号       | 封装        | 封装尺寸 (标称值)      |

|------------|-----------|-----------------|

| bq40z50-R2 | VQFN (32) | 4.00mm x 4.00mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

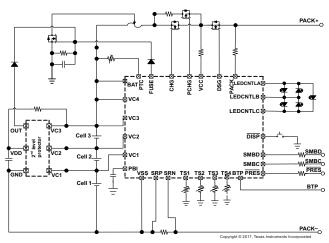

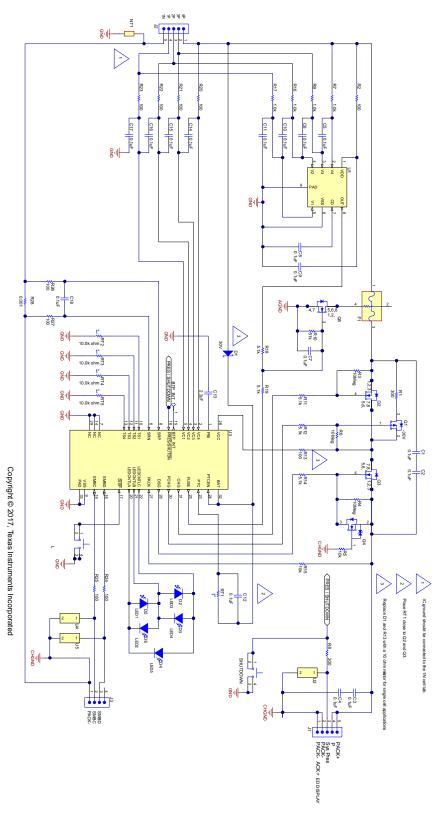

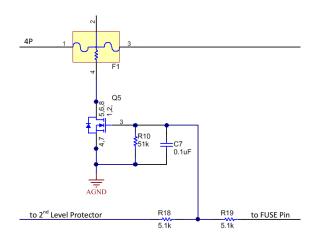

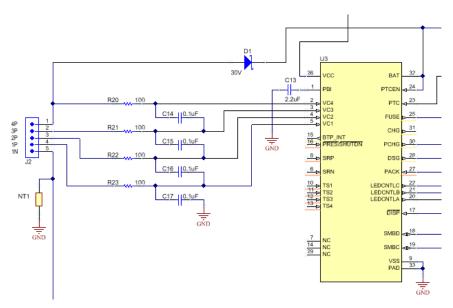

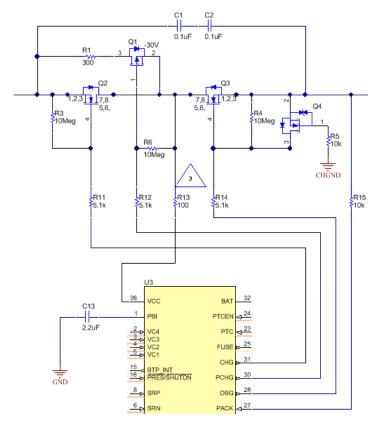

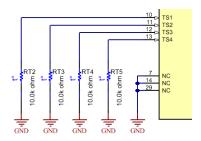

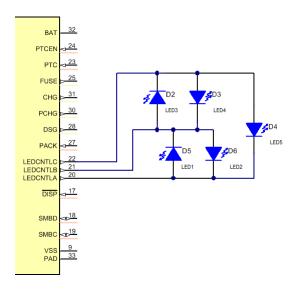

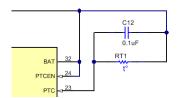

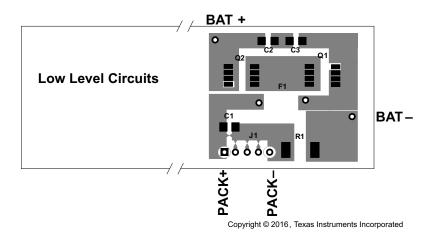

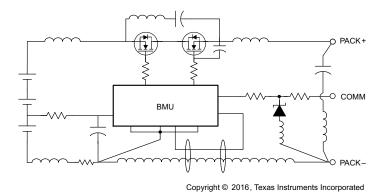

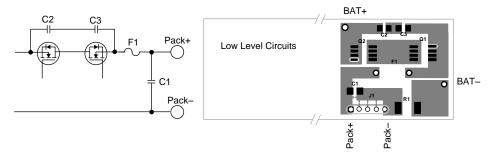

### 简化电路原理图

## 目录

| 4 | 4± M-                                  |    | 7.26 Low-Frequency Oscillator                              | 1.1 |

|---|----------------------------------------|----|------------------------------------------------------------|-----|

| 1 | 特性1                                    |    | 7.26 Low-Frequency Oscillator                              |     |

| 2 | 应用1                                    |    | •                                                          |     |

| 3 | 说明 1                                   |    |                                                            |     |

| 4 | 修订历史记录 2                               |    | 7.29 Instruction Flash                                     |     |

| 5 | 说明 (续)2                                |    | 7.30 Data Flash                                            | 15  |

| 6 | Pin Configuration and Functions 3      |    | 7.31 OCD, SCC, SCD1, SCD2 Current Protection<br>Thresholds | 16  |

| 7 | Specifications7                        |    | 7.32 Timing Requirements: OCD, SCC, SCD1, SCD2             | 2   |

|   | 7.1 Absolute Maximum Ratings 7         |    | Current Protection Timing                                  |     |

|   | 7.2 ESD Ratings 7                      |    | 7.33 Timing Requirements: SMBus                            | 17  |

|   | 7.3 Recommended Operating Conditions 8 |    | 7.34 Timing Requirements: SMBus XL                         | 17  |

|   | 7.4 Thermal Information8               |    | 7.35 Typical Characteristics                               | 19  |

|   | 7.5 Supply Current 8                   | 8  | Detailed Description                                       | 22  |

|   | 7.6 Power Supply Control9              |    | 8.1 Overview                                               | 22  |

|   | 7.7 AFE Power-On Reset9                |    | 8.2 Functional Block Diagram                               | 22  |

|   | 7.8 AFE Watchdog Reset and Wake Timer9 |    | 8.3 Feature Description                                    | 23  |

|   | 7.9 Current Wake Comparator9           |    | 8.4 Device Functional Modes                                | 26  |

|   | 7.10 VC1, VC2, VC3, VC4, BAT, PACK     | 9  | Application and Implementation                             | 27  |

|   | 7.11 SMBD, SMBC 10                     |    | 9.1 Application Information                                |     |

|   | 7.12 PRES, BTP_INT, DISP 10            |    | 9.2 Typical Applications                                   |     |

|   | 7.13 LEDCNTLA, LEDCNTLB, LEDCNTLC11    | 10 | Power Supply Recommendations                               |     |

|   | 7.14 Coulomb Counter                   | 11 | Layout                                                     |     |

|   | 7.15 CC Digital Filter11               |    | 11.1 Layout Guidelines                                     |     |

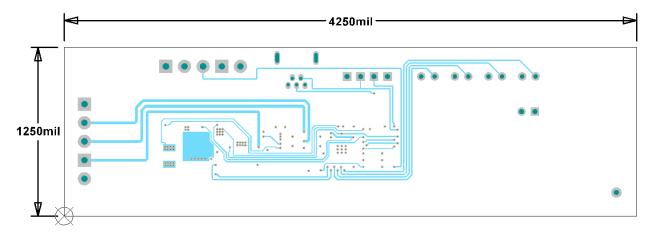

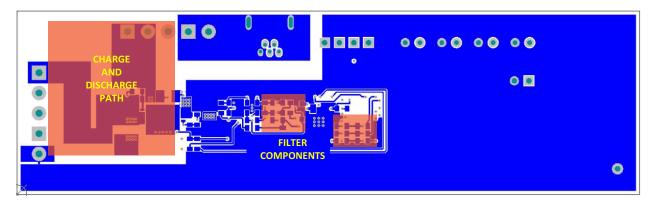

|   | 7.16 ADC11                             |    | 11.2 Layout Example                                        |     |

|   | 7.17 ADC Digital Filter 12             | 12 | 器件和文档支持                                                    |     |

|   | 7.18 CHG, DSG FET Drive                |    | 12.1 文档支持                                                  |     |

|   | 7.19 PCHG FET Drive                    |    | <b>12.2</b> 接收文档更新通知                                       |     |

|   | 7.20 FUSE Drive                        |    | 12.3 社区资源                                                  |     |

|   | 7.21 Internal Temperature Sensor       |    | 12.4 商标                                                    |     |

|   | 7.22 TS1, TS2, TS3, TS4 13             |    | 12.5 静电放电警告                                                |     |

|   | 7.23 PTC, PTCEN 14                     |    | 12.6 Glossary                                              |     |

|   | 7.24 Internal 1.8-V LDO 14             | 13 | 机械、封装和可订购信息                                                |     |

|   | 7.25 High-Frequency Oscillator         | 13 | 少的人, 五人人人,一只 人,人们 一只 人,一                                   | 43  |

|   |                                        |    |                                                            |     |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

### Changes from Original (June 2017) to Revision A

**Page**

## 5 说明 (续)

bq40z50-R2 器件为主机系统提供可用的最大功率和最大电流,从而支持TURBO模式 2.0。该器件还支持电池跳闸,从而在预设的充电阈值状态向主机系统发送 BTP 中断信号。

bq40z50-R2 提供了基于软件的第 1 级和第 2 级安全保护,可应对过压、欠压、过流、短路、过载和过热情况以及其他与电池组和电池相关的故障。

SHA-1 认证对认证码密钥使用安全存储器,确保识别真正的电池组。

紧凑的 32 引脚 QFN 封装在大大降低解决方案成本并减小解决方案尺寸的同时,最大限度地为电池监测 应用提供了功能性与安全性。

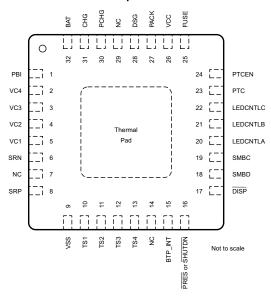

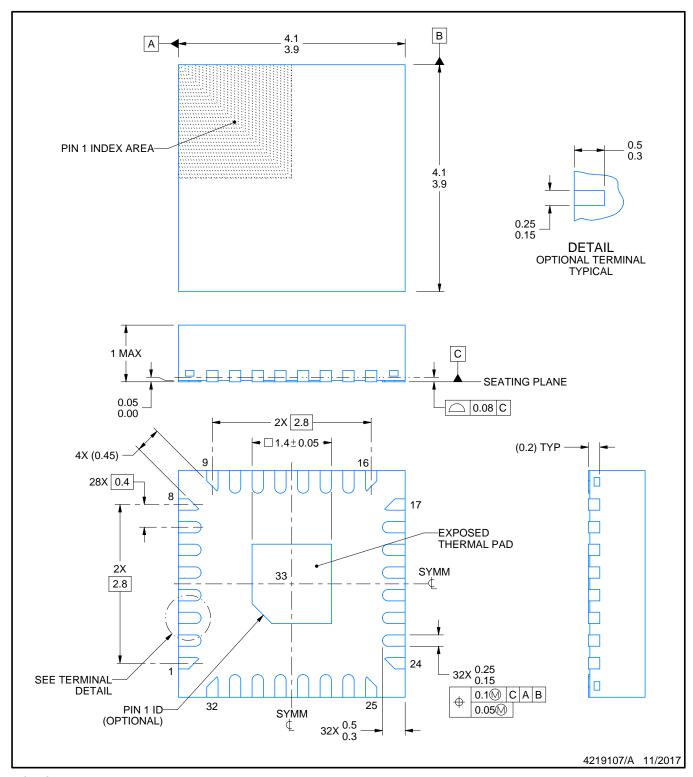

# 6 Pin Configuration and Functions

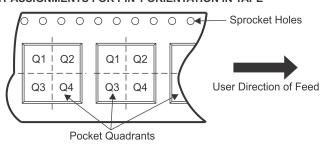

#### RSM Package 32-Pin VQFN with Exposed Thermal Pad Top View

#### **Pin Functions**

| PIN NUMBER | PIN NAME       | TYPE             | DESCRIPTION                                                                                                                                                                    |

|------------|----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | PBI            | P <sup>(1)</sup> | Power supply backup input pin                                                                                                                                                  |

| 2          | VC4            | IA               | Sense voltage input pin for the most positive cell, and balance current input for the most positive cell                                                                       |

| 3          | VC3            | IA               | Sense voltage input pin for the second-most positive cell, balance current input for the second-most positive cell, and return balance current for the most positive cell      |

| 4          | VC2            | IA               | Sense voltage input pin for the third-most positive cell, balance current input for the third-most positive cell, and return balance current for the second-most positive cell |

| 5          | VC1            | IA               | Sense voltage input pin for the least positive cell, balance current input for the least positive cell, and return balance current for the third-most positive cell            |

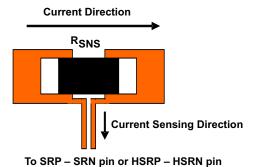

| 6          | SRN            | I                | Analog input pin connected to the internal coulomb counter peripheral for integrating a small voltage between SRP and SRN where SRP is the top of the sense resistor.          |

| 7          | NC             | _                | Not internally connected                                                                                                                                                       |

| 8          | SRP            | I                | Analog input pin connected to the internal coulomb counter peripheral for integrating a small voltage between SRP and SRN where SRP is the top of the sense resistor.          |

| 9          | VSS            | Р                | Device ground                                                                                                                                                                  |

| 10         | TS1            | IA               | Temperature sensor 1 thermistor input pin                                                                                                                                      |

| 11         | TS2            | IA               | Temperature sensor 2 thermistor input pin                                                                                                                                      |

| 12         | TS3            | IA               | Temperature sensor 3 thermistor input pin                                                                                                                                      |

| 13         | TS4            | IA               | Temperature sensor 4 thermistor input pin                                                                                                                                      |

| 14         | NC             | _                | Not internally connected                                                                                                                                                       |

| 15         | BTP_INT        | 0                | Battery Trip Point (BTP) interrupt output                                                                                                                                      |

| 16         | PRES or SHUTDN | I                | Host system present input for removable battery pack or emergency system shutdown input for embedded pack. A pullup is not required for this pin.                              |

| 17         | DISP           | -                | Display control for LEDs                                                                                                                                                       |

(1) P = Power Connection, O = Digital Output, AI = Analog Input, I = Digital Input, I/OD = Digital Input/Output

# Pin Functions (continued)

| PIN NUMBER | PIN NAME | TYPE | DESCRIPTION                                                                                            |

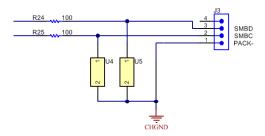

|------------|----------|------|--------------------------------------------------------------------------------------------------------|

| 18         | SMBD     | I/OD | SMBus data pin                                                                                         |

| 19         | SMBC     | I/OD | SMBus clock pin                                                                                        |

| 20         | LEDCNTLA | _    | LED display segment that drives the external LEDs depending on the firmware configuration              |

| 21         | LEDCNTLB | _    | LED display segment that drives the external LEDs depending on the firmware configuration              |

| 22         | LEDCNTLC | _    | LED display segment that drives the external LEDs depending on the firmware configuration              |

| 23         | PTC      | IA   | Safety PTC thermistor input pin. To disable, connect both PTC and PTCEN to VSS.                        |

| 24         | PTCEN    | IA   | Safety PTC thermistor enable input pin. Connect to BAT. To disable, connect both PTC and PTCEN to VSS. |

| 25         | FUSE     | 0    | Fuse drive output pin. Connect to VSS if not used.                                                     |

| 26         | VCC      | Р    | Secondary power supply input                                                                           |

| 27         | PACK     | IA   | Pack sense input pin                                                                                   |

| 28         | DSG      | 0    | NMOS Discharge FET drive output pin                                                                    |

| 29         | NC       | _    | Not internally connected                                                                               |

| 30         | PCHG     | 0    | PMOS Precharge FET drive output pin                                                                    |

| 31         | CHG      | 0    | NMOS Charge FET drive output pin                                                                       |

| 32         | BAT      | Р    | Primary power supply input pin                                                                         |

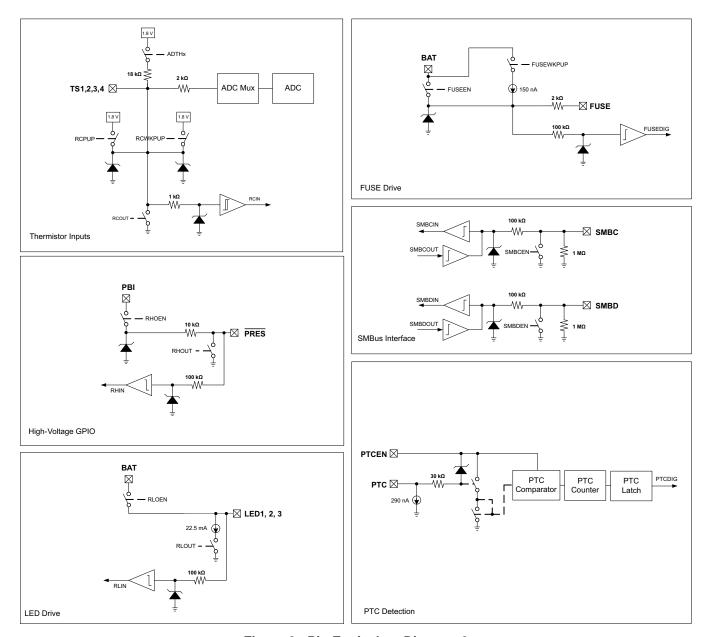

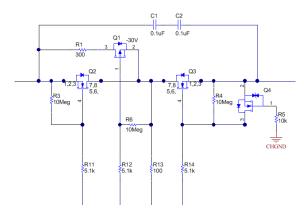

Figure 1. Pin Equivalent Diagram 1

Figure 2. Pin Equivalent Diagram 2

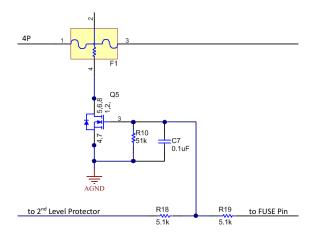

Figure 3. Pin Equivalent Diagram 3

# 7 Specifications

## 7.1 Absolute Maximum Ratings

Over-operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                       |                                                 | MIN       | MAX                       | UNIT |

|---------------------------------------|-------------------------------------------------|-----------|---------------------------|------|

| Supply voltage range, V <sub>CC</sub> | BAT, VCC, PBI                                   | -0.3      | 30                        | V    |

|                                       | PACK, SMBC, SMBD, PRES or SHUTDN, BTP_INT, DISP | -0.3      | 30                        | V    |

|                                       | TS1, TS2, TS3, TS4                              | -0.3      | $V_{REG} + 0.3$           | V    |

|                                       | PTC, PTCEN, LEDCNTLA, LEDCNTLB, LEDCNTLC        | -0.3      | $V_{BAT} + 0.3$           | V    |

|                                       | SRP, SRN                                        | -0.3      | 0.3                       | V    |

| Input voltage range,                  | VC4                                             | VC3 - 0.3 | VC3 + 8.5, or<br>VSS + 30 | V    |

| $V_{IN}$                              | VC3                                             | VC2 - 0.3 | VC2 + 8.5, or<br>VSS + 30 | V    |

|                                       | VC2                                             | VC1 - 0.3 | VC1 + 8.5, or<br>VSS + 30 | V    |

|                                       | VC1                                             | VSS - 0.3 | VSS + 8.5, or<br>VSS + 30 | V    |

| Output voltage range,                 | CHG, DSG                                        | -0.3      | 32                        |      |

| Vo                                    | PCHG, FUSE                                      | -0.3      | 30                        | V    |

| Maximum VSS current,                  | ximum VSS current, I <sub>SS</sub>              |           | 50                        | mA   |

| Storage temperature, T <sub>STG</sub> |                                                 | -65       | 150                       | °C   |

| Lead temperature (sold                | ering, 10 s), T <sub>SOLDER</sub>               |           | 300                       | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |               |                                                                     | VALUE | UNIT |

|--------------------|---------------|---------------------------------------------------------------------|-------|------|

| .,                 | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                         |                             |                                                              | MIN              | NOM  | MAX                  | UNIT |

|-------------------------|-----------------------------|--------------------------------------------------------------|------------------|------|----------------------|------|

| V <sub>CC</sub>         | Supply voltage              | BAT, VCC, PBI                                                | 2.2              |      | 26                   | V    |

| V <sub>SHUTDOWN</sub> - | Shutdown voltage            | V <sub>PACK</sub> < V <sub>SHUTDOWN</sub> -                  | 1.8              | 2.0  | 2.2                  | V    |

| V <sub>SHUTDOWN+</sub>  | Start-up voltage            | V <sub>PACK</sub> > V <sub>SHUTDOWN</sub> + V <sub>HYS</sub> | 2.05             | 2.25 | 2.45                 | V    |

| V <sub>HYS</sub>        | Shutdown voltage hysteresis | V <sub>SHUTDOWN+</sub> - V <sub>SHUTDOWN-</sub>              |                  | 250  |                      | mV   |

|                         |                             | PACK, SMBC, SMBD, PRES, BTP_IN, DISP                         |                  |      | 26                   |      |

|                         | Input voltage range         | TS1, TS2, TS3, TS4                                           |                  |      | $V_{REG}$            |      |

|                         |                             | PTC, PTCEN, LEDCNTLA, LEDCNTLB, LEDCNTLC                     |                  |      | $V_{BAT}$            |      |

| V                       |                             | SRP, SRN                                                     | -0.2             |      | 0.2                  | V    |

| V <sub>IN</sub>         |                             | VC4                                                          | V <sub>VC3</sub> |      | V <sub>VC3</sub> + 5 | V    |

|                         |                             | VC3                                                          | $V_{VC2}$        |      | V <sub>VC2</sub> + 5 |      |

|                         |                             | VC2                                                          | V <sub>VC1</sub> |      | V <sub>VC1</sub> + 5 |      |

|                         |                             | VC1                                                          | V <sub>VSS</sub> |      | $V_{VSS} + 5$        |      |

| Vo                      | Output voltage range        | CHG, DSG, PCHG, FUSE                                         |                  |      | 26                   | V    |

| C <sub>PBI</sub>        | External PBI capacitor      |                                                              | 2.2              |      |                      | μF   |

| T <sub>OPR</sub>        | Operating temperature       |                                                              | -40              |      | 85                   | °C   |

## 7.4 Thermal Information

|                          |                                              | bq40z50-R2 |      |

|--------------------------|----------------------------------------------|------------|------|

|                          | THERMAL METRIC <sup>(1)</sup>                | RSM (QFN)  | UNIT |

|                          |                                              | 32 PINS    |      |

| R <sub>θJA, High K</sub> | Junction-to-ambient thermal resistance       | 47.4       | °C/W |

| $R_{\theta JC(top)}$     | Junction-to-case(top) thermal resistance     | 40.3       | °C/W |

| $R_{\theta JB}$          | Junction-to-board thermal resistance         | 14.7       | °C/W |

| ΤιΨ                      | Junction-to-top characterization parameter   | 0.8        | °C/W |

| ΨЈВ                      | Junction-to-board characterization parameter | 14.4       | °C/W |

| $R_{\theta JC(bottom)}$  | Junction-to-case(bottom) thermal resistance  | 3.8        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 7.5 Supply Current

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 20 V (unless otherwise noted)

|                               | PARAMETER                              | TEST CONDITIONS                       | MIN | TYP | MAX | UNIT |

|-------------------------------|----------------------------------------|---------------------------------------|-----|-----|-----|------|

| I <sub>NORMAL</sub>           | NORMAL mode                            | CHG on. DSG on, no Flash write        |     | 336 |     | μA   |

|                               | CL EED made                            | CHG off, DSG on, no SBS communication |     | 75  |     |      |

| I <sub>SLEEP</sub> SLEEP mode | CHG off, DSG off, no SBS communication |                                       | 52  |     | μA  |      |

| I <sub>SHUTDOWN</sub>         | SHUTDOWN mode                          |                                       |     | 1.6 |     | μA   |

## 7.6 Power Supply Control

Typical values stated where  $T_A = 25$ °C and VCC = 14.4 V, Min/Max values stated where  $T_A = -40$ °C to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| PAR                       | AMETER                                          | TEST CONDITIONS                                                      | MIN  | TYP  | MAX  | UNIT |

|---------------------------|-------------------------------------------------|----------------------------------------------------------------------|------|------|------|------|

| V <sub>SWITCHOVER</sub> - | BAT to V <sub>CC</sub><br>switchover<br>voltage | V <sub>BAT</sub> < V <sub>SWITCHOVER</sub> -                         | 1.95 | 2.1  | 2.2  | V    |

| V <sub>SWITCHOVER+</sub>  | V <sub>CC</sub> to BAT<br>switchover<br>voltage | V <sub>BAT</sub> > V <sub>SWITCHOVER</sub> + V <sub>HYS</sub>        | 2.9  | 3.1  | 3.25 | V    |

| V <sub>HYS</sub>          | Switchover voltage hysteresis                   | V <sub>SWITCHOVER+</sub> - V <sub>SWITCHOVER-</sub>                  |      | 1000 |      | mV   |

|                           |                                                 | BAT pin, BAT = 0 V, VCC = 25 V, PACK = 25 V                          |      |      | 1    |      |

| $I_{LKG}$                 | Input Leakage current                           | PACK pin, BAT = 25 V, VCC = 0 V, PACK = 0 V                          |      |      | 1    | μA   |

|                           |                                                 | BAT and PACK terminals, BAT = 0 V, VCC = 0 V, PACK = 0 V, PBI = 25 V |      |      | 1    | μΛ   |

#### 7.7 AFE Power-On Reset

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                    | PARAMETER                    | TEST CONDITIONS                           | MIN  | TYP  | MAX  | UNIT |

|--------------------|------------------------------|-------------------------------------------|------|------|------|------|

| V <sub>REGIT</sub> | Negative-going voltage input | V <sub>REG</sub>                          | 1.51 | 1.55 | 1.59 | V    |

| V <sub>HYS</sub>   | Power-on reset hysteresis    | V <sub>REGIT+</sub> - V <sub>REGIT-</sub> | 70   | 100  | 130  | mV   |

| t <sub>RST</sub>   | Power-on reset time          |                                           | 200  | 300  | 400  | μs   |

## 7.8 AFE Watchdog Reset and Wake Timer

Typical values stated where  $T_A = 25^{\circ}$ C and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}$ C to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                     | PARAMETER                 | TEST CONDITIONS           | MIN  | TYP  | MAX  | UNIT |

|---------------------|---------------------------|---------------------------|------|------|------|------|

|                     |                           | t <sub>WDT</sub> = 500    | 372  | 500  | 628  |      |

|                     | AFE watchdog              | t <sub>WDT</sub> = 1000   | 744  | 1000 | 1256 |      |

| t <sub>WDT</sub>    | timeout                   | t <sub>WDT</sub> = 2000   | 1488 | 2000 | 2512 | ms   |

|                     |                           | t <sub>WDT</sub> = 4000   | 2976 | 4000 | 5024 |      |

|                     |                           | t <sub>WAKE</sub> = 250   | 186  | 250  | 314  |      |

|                     | AFF wales times           | t <sub>WAKE</sub> = 500   | 372  | 500  | 628  |      |

| t <sub>WAKE</sub>   | AFE wake timer            | t <sub>WAKE</sub> = 1000  | 744  | 1000 | 1256 | ms   |

|                     |                           | t <sub>WAKE</sub> = 512   | 1488 | 2000 | 2512 |      |

| t <sub>FETOFF</sub> | FET off delay after reset | t <sub>FETOFF</sub> = 512 | 409  | 512  | 614  | ms   |

## 7.9 Current Wake Comparator

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| PA                       | RAMETER                                         | TEST CONDITIONS                   | MIN  | TYP    | MAX  | UNIT |

|--------------------------|-------------------------------------------------|-----------------------------------|------|--------|------|------|

| V                        |                                                 | $V_{WAKE} = \pm 0.625 \text{ mV}$ | ±0.3 | ±0.625 | ±0.9 |      |

|                          | Wake voltage                                    | $V_{WAKE} = \pm 1.25 \text{ mV}$  | ±0.6 | ±1.25  | ±1.8 | m\/  |

| $V_{WAKE}$               | threshold                                       | $V_{WAKE} = \pm 2.5 \text{ mV}$   | ±1.2 | ±2.5   | ±3.6 | mV   |

|                          |                                                 | V <sub>WAKE</sub> = ±5 mV         | ±2.4 | ±5.0   | ±7.2 |      |

| V <sub>WAKE(DRIFT)</sub> | Temperature drift of V <sub>WAKE</sub> accuracy |                                   |      | 0.5%   |      | °C   |

### **Current Wake Comparator (continued)**

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                       | PARAMETER                                                   | TEST CONDITIONS | MIN | TYP | MAX  | UNIT |

|-----------------------|-------------------------------------------------------------|-----------------|-----|-----|------|------|

| t <sub>WAKE</sub>     | Time from<br>application of<br>current to wake<br>interrupt |                 |     |     | 700  | μs   |

| t <sub>WAKE(SU)</sub> | Wake comparator<br>startup time                             |                 |     | 500 | 1000 | μs   |

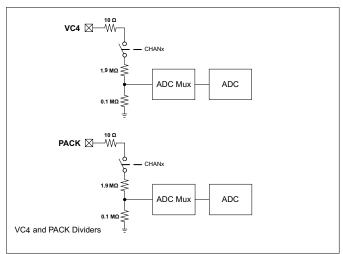

### 7.10 VC1, VC2, VC3, VC4, BAT, PACK

Typical values stated where  $T_A = 25^{\circ}$ C and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}$ C to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                  | PARAMETER                           | TEST CONDITIONS                                                                        | MIN    | TYP    | MAX    | UNIT |

|------------------|-------------------------------------|----------------------------------------------------------------------------------------|--------|--------|--------|------|

|                  |                                     | VC1-VSS, VC2-VC1, VC3-VC2, VC4-VC3                                                     | 0.1980 | 0.2000 | 0.2020 |      |

| K                | K Scaling factor                    | BAT-VSS, PACK-VSS                                                                      | 0.049  | 0.050  | 0.051  | _    |

|                  |                                     | V <sub>REF2</sub>                                                                      | 0.490  | 0.500  | 0.510  |      |

| V                | lanut voltage renge                 | VC1-VSS, VC2-VC1, VC3-VC2, VC4-VC3                                                     | -0.2   |        | 5      | V    |

| VIN              | V <sub>IN</sub> Input voltage range | BAT-VSS, PACK-VSS                                                                      | -0.2   |        | 20     |      |

| I <sub>LKG</sub> | Input leakage current               | VC1, VC2, VC3, VC4, cell balancing off, cell detach detection off, ADC multiplexer off |        |        | 1      | μΑ   |

| R <sub>CB</sub>  | Internal cell balance resistance    | R <sub>DS(ON)</sub> for internal FET switch at 2 V < V <sub>DS</sub> < 4 V             |        |        | 200    | Ω    |

| I <sub>CD</sub>  | Internal cell detach check current  | VCx > VSS + 0.8 V                                                                      | 30     | 50     | 70     | μΑ   |

### 7.11 SMBD, SMBC

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                 | ( (                   |                                                                   |     |     |     |      |

|-----------------|-----------------------|-------------------------------------------------------------------|-----|-----|-----|------|

|                 | PARAMETER             | TEST CONDITIONS                                                   | MIN | TYP | MAX | UNIT |

| $V_{IH}$        | Input voltage high    | SMBC, SMBD, V <sub>REG</sub> = 1.8 V                              | 1.3 |     |     | V    |

| $V_{IL}$        | Input voltage low     | SMBC, SMBD, V <sub>REG</sub> = 1.8 V                              |     |     | 8.0 | V    |

| V <sub>OL</sub> | Output low voltage    | SMBC, SMBD, $V_{REG} = 1.8 \text{ V}$ , $I_{OL} = 1.5 \text{ mA}$ |     |     | 0.4 | V    |

| C <sub>IN</sub> | Input capacitance     |                                                                   |     | 5   |     | pF   |

| $I_{LKG}$       | Input leakage current |                                                                   |     |     | 1   | μΑ   |

| R <sub>PD</sub> | Pulldown resistance   |                                                                   | 0.7 | 1.0 | 1.3 | ΜΩ   |

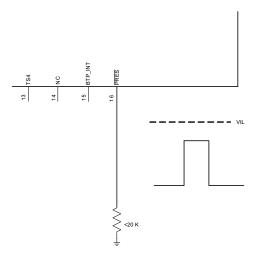

# 7.12 PRES, BTP\_INT, DISP

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                 | PARAMETER                 | TEST CONDITIONS                                     | MIN | TYP | MAX  | UNIT |

|-----------------|---------------------------|-----------------------------------------------------|-----|-----|------|------|

| $V_{IH}$        | High-level input          |                                                     | 1.3 |     |      | V    |

| $V_{IL}$        | Low-level input           |                                                     |     |     | 0.55 | V    |

| \/              | Output voltage high       | $V_{BAT} > 5.5 \text{ V}, I_{OH} = -0 \mu A$        | 3.5 |     |      | V    |

| V <sub>OH</sub> | Output voltage high       | $V_{BAT} > 5.5 \text{ V}, I_{OH} = -10 \mu\text{A}$ | 1.8 |     |      | V    |

| $V_{OL}$        | Output voltage low        | I <sub>OL</sub> = 1.5 mA                            |     |     | 0.4  | V    |

| C <sub>IN</sub> | Input capacitance         |                                                     |     | 5   |      | pF   |

| $I_{LKG}$       | Input leakage current     |                                                     |     |     | 1    | μΑ   |

| R <sub>O</sub>  | Output reverse resistance | Between PRES or BTP_INT or DISP and PBI             | 8   |     |      | kΩ   |

## 7.13 LEDCNTLA, LEDCNTLB, LEDCNTLC

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                       | PARAMETER                            | TEST CONDITIONS                                      | MIN                       | TYP  | MAX         | UNIT |

|-----------------------|--------------------------------------|------------------------------------------------------|---------------------------|------|-------------|------|

| V <sub>IH</sub>       | High-level input                     |                                                      | 1.45                      |      |             | V    |

| V <sub>IL</sub>       | Low-level input                      |                                                      |                           |      | 0.55        | V    |

| V <sub>OH</sub>       | Output voltage high                  | $V_{BAT} > 3.0 \text{ V}, I_{OH} = -22.5 \text{ mA}$ | V <sub>BAT</sub> –<br>1.6 |      |             | V    |

| V <sub>OL</sub>       | Output voltage low                   | I <sub>OL</sub> = 1.5 mA                             |                           |      | 0.4         | V    |

| I <sub>SC</sub>       | High level output current protection |                                                      | -30                       | -45  | <b>-6</b> 0 | mA   |

| I <sub>OL</sub>       | Low level output current             | V <sub>BAT</sub> > 3.0 V, V <sub>OH</sub> = 0.4 V    | 15.75                     | 22.5 | 29.25       | mA   |

| I <sub>LEDCNTLx</sub> | Current matching between LEDCNTLx    | V <sub>BAT</sub> = V <sub>LEDCNTLx</sub> + 2.5 V     |                           | ±1%  |             |      |

| C <sub>IN</sub>       | Input capacitance                    |                                                      |                           | 20   |             | pF   |

| I <sub>LKG</sub>      | Input leakage current                |                                                      |                           |      | 1           | μΑ   |

| f <sub>LEDCNTLx</sub> | Frequency of LED pattern             |                                                      |                           | 124  |             | Hz   |

#### 7.14 Coulomb Counter

Typical values stated where  $T_A = 25$ °C and VCC = 14.4 V, Min/Max values stated where  $T_A = -40$ °C to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| 2.2 V to 20 V (dilicos otrici | , , , , , , , , , , , , , , , , , , ,     |                        |       |                       |        |

|-------------------------------|-------------------------------------------|------------------------|-------|-----------------------|--------|

| PARAMETER                     | TEST CONDITIONS                           | MIN                    | TYP   | MAX                   | UNIT   |

| Input voltage range           |                                           | -0.1                   |       | 0.1                   | V      |

| Full scale range              |                                           | -V <sub>REF1</sub> /10 |       | V <sub>REF1</sub> /10 | V      |

| Integral nonlinearity (1)     | 16-bit, best fit over input voltage range |                        | ±5.2  | ±22.3                 | LSB    |

| Offset error                  | 16-bit, Post-calibration                  |                        | ±5    | ±10                   | μV     |

| Offset error drift            | 15-bit + sign, Post-calibration           |                        | 0.2   | 0.3                   | μV/°C  |

| Gain error                    | 15-bit + sign, over input voltage range   |                        | ±0.2% | ±0.8%                 | FSR    |

| Gain error drift              | 15-bit + sign, over input voltage range   |                        |       | 150                   | PPM/°C |

| Effective input resistance    |                                           | 2.5                    |       |                       | МΩ     |

<sup>(1) 1</sup> LSB =  $V_{REF1}/(10 \times 2^N) = 1.215/(10 \times 2^{15}) = 3.71 \ \mu V$

## 7.15 CC Digital Filter

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| PARAMETER            | TEST CONDITIONS   | MIN | TYP | MAX | UNIT |

|----------------------|-------------------|-----|-----|-----|------|

| Conversion time      | Single conversion |     | 250 |     | ms   |

| Effective resolution | Single conversion | 15  |     |     | Bits |

### 7.16 ADC

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| PARAMETER                            | TEST CONDITIONS                                     | MIN              | TYP MAX              | UNIT |

|--------------------------------------|-----------------------------------------------------|------------------|----------------------|------|

| longit voltage renge                 | Internal reference (V <sub>REF1</sub> )             | -0.2             | 1                    | V    |

| Input voltage range                  | External reference (V <sub>REG</sub> )              | -0.2             | $0.8 \times V_{REG}$ | V    |

| Full scale range                     | $V_{FS} = V_{REF1}$ or $V_{REG}$                    | -V <sub>FS</sub> | $V_{FS}$             | V    |

| Integral popling ority (1)           | 16-bit, best fit, -0.1 V to 0.8 × V <sub>REF1</sub> |                  | ±6.6                 | LSB  |

| Integral nonlinearity <sup>(1)</sup> | 16-bit, best fit, -0.2 V to -0.1 V                  |                  | ±13.1                | LOD  |

(1) 1 LSB =  $V_{REF1}/(2^N)$  = 1.225/(2<sup>15</sup>) = 37.4  $\mu$ V (when  $t_{CONV}$  = 31.25 ms)

## **ADC** (continued)

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| PARAMETER                   | TEST CONDITIONS                                               | MIN | TYP   | MAX   | UNIT   |

|-----------------------------|---------------------------------------------------------------|-----|-------|-------|--------|

| Offset error <sup>(2)</sup> | 16-bit, Post-calibration, V <sub>FS</sub> = V <sub>REF1</sub> |     | ±67   | ±157  | μV     |

| Offset error drift          | 16-bit, Post-calibration, V <sub>FS</sub> = V <sub>REF1</sub> |     | 0.6   | 3     | μV/°C  |

| Gain error                  | 16-bit, -0.1 V to 0.8 × V <sub>FS</sub>                       |     | ±0.2% | ±0.8% | FSR    |

| Gain error drift            | 16-bit, -0.1 V to 0.8 × V <sub>FS</sub>                       |     |       | 150   | PPM/°C |

| Effective input resistance  |                                                               | 8   |       |       | ΜΩ     |

<sup>(2)</sup> For VC1–VSS, VC2–VC1, VC3–VC2, VC4–VC3, VC4–VSS, PACK–VSS, and V<sub>REF1</sub>/2, the offset error is multiplied by (1/ADC multiplexer scaling factor (K)).

## 7.17 ADC Digital Filter

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| PARAMETER            | TEST CONDITIONS                         | MIN | TYP   | MAX | UNIT |

|----------------------|-----------------------------------------|-----|-------|-----|------|

|                      | Single conversion                       |     | 31.25 |     |      |

| Conversion time      | Single conversion                       |     | 15.63 |     | ma   |

|                      | Single conversion                       |     | 7.81  |     | ms   |

|                      | Single conversion                       |     | 1.95  |     |      |

| Resolution           | No missing codes                        | 16  |       |     | Bits |

|                      | With sign, t <sub>CONV</sub> = 31.25 ms | 14  | 15    |     |      |

| Effective resolution | With sign, t <sub>CONV</sub> = 15.63 ms | 13  | 14    |     | Bits |

| Effective resolution | With sign, t <sub>CONV</sub> = 7.81 ms  | 11  | 12    |     |      |

|                      | With sign, t <sub>CONV</sub> = 1.95 ms  | 9   | 10    |     |      |

### 7.18 CHG, DSG FET Drive

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| PAI                    | RAMETER                                                | TEST CONDITIONS                                                                                                                                                                 | MIN   | TYP   | MAX   | UNIT |

|------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

|                        | Output voltage                                         | Ratio_{DSG} = (V_{DSG} - V_{BAT})/V_{BAT}, 2.2 V < V_{BAT} < 4.92 V, 10 M $\Omega$ between PACK and DSG                                                                         | 2.133 | 2.333 | 2.433 |      |

|                        | ratio                                                  | Ratio <sub>CHG</sub> = (V <sub>CHG</sub> – V <sub>BAT</sub> )/V <sub>BAT</sub> , 2.2 V < V <sub>BAT</sub> < 4.92 V, 10 M $\Omega$ between BAT and CHG                           | 2.133 | 2.333 | 2.433 | _    |

| V                      | V <sub>(FETON)</sub> Output voltage,<br>CHG and DSG on | $V_{\rm DSG(ON)} = V_{\rm DSG} - V_{\rm BAT}, \ V_{\rm BAT} \ge 4.92 \ \rm V, \ 10 \ M\Omega$ between PACK and DSG, $V_{\rm BAT} = 18 \ \rm V$                                  | 10.5  | 11.5  | 12    | V    |

| V (FETON)              |                                                        | $V_{CHG(ON)} = V_{CHG} - V_{BAT}, V_{BAT} \ge 4.92$ V, 10 MΩ between BAT and CHG, $V_{BAT} = 18$ V                                                                              | 10.5  | 11.5  | 12    | V    |

| V <sub>(FETOFF)</sub>  | Output voltage,                                        | $V_{DSG(OFF)}$ = $V_{DSG} - V_{PACK},~10~\text{M}\Omega$ between PACK and DSG                                                                                                   | -0.4  |       | 0.4   | V    |

| , ,                    | *(FETOFF) CHG and DSG off                              | $V_{CHG(OFF)} = V_{CHG} - V_{BAT}$ , 10 M $\Omega$ between BAT and CHG                                                                                                          | -0.4  |       | 0.4   |      |

|                        |                                                        | $V_{DSG}$ from 0% to 35% $V_{DSG(ON)(TYP)}$ , $V_{BAT}$ ≥ 2.2 V, $C_L$ = 4.7 nF between DSG and PACK, 5.1 kΩ between DSG and $C_L$ , 10 MΩ between PACK and DSG                 |       | 200   | 500   | 110  |

| t <sub>R</sub>         | Rise time                                              | $V_{CHG}$ from 0% to 35% $V_{CHG(ON)(TYP)}$ , $V_{BAT} \ge 2.2$ V, $C_L = 4.7$ nF between CHG and BAT, 5.1 k $\Omega$ between CHG and $C_L$ , 10 M $\Omega$ between BAT and CHG |       | 200   | 500   | μs   |

| t <sub>F</sub> Fall ti | Fall time                                              | $V_{DSG}$ from $V_{DSG(ON)(TYP)}$ to 1 V, $V_{BAT}$ ≥ 2.2 V, $C_L$ = 4.7 nF between DSG and PACK, 5.1 kΩ between DSG and $C_L$ , 10 MΩ between PACK and DSG                     |       | 40    | 300   |      |

|                        | rail liffle                                            | $V_{CHG}$ from $V_{CHG(ON)(TYP)}$ to 1 V, $V_{BAT}$ ≥ 2.2 V, $C_L$ = 4.7 nF between CHG and BAT, 5.1 kΩ between CHG and $C_L$ , 10 MΩ between BAT and CHG                       |       | 40    | 200   | μs   |

## 7.19 PCHG FET Drive

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| P.A                   | RAMETER                  | TEST CONDITIONS                                                                                                                                                             | MIN  | TYP | MAX | UNIT |

|-----------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| V <sub>(FETON)</sub>  | Output voltage, PCHG on  | $V_{PCHG(ON)}$ = $VV_{CC}$ – $V_{PCHG},~10~M\Omega$ between $V_{CC}$ and PCHG                                                                                               | 6    | 7   | 8   | V    |

| V <sub>(FETOFF)</sub> | Output voltage, PCHG off | $V_{PCHG(OFF)}$ = $VV_{CC}$ – $V_{PCHG}$ , 10 M $\Omega$ between $V_{CC}$ and PCHG                                                                                          | -0.4 |     | 0.4 | V    |

| t <sub>R</sub>        | Rise time                | $V_{PCHG}$ from 10% to 90% $V_{PCHG(ON)(TYP)}$ , $VV_{CC}$ ≥ 8 V, $C_L$ = 4.7 nF between PCHG and $V_{CC}$ , 5.1 kΩ between PCHG and $C_L$ , 10 MΩ between $V_{CC}$ and CHG |      | 40  | 200 | μs   |

| t <sub>F</sub>        | Fall time                | $V_{PCHG}$ from 90% to 10% $V_{PCHG(ON)(TYP)}$ , $V_{CC}$ ≥ 8 V, $C_L$ = 4.7 nF between PCHG and $V_{CC}$ , 5.1 kΩ between PCHG and $C_L$ , 10 MΩ between $V_{CC}$ and CHG  |      | 40  | 200 | μs   |

#### 7.20 FUSE Drive

Typical values stated where  $T_A = 25^{\circ}$ C and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}$ C to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| PA                       | RAMETER                   | TEST CONDITIONS                                                             | MIN                    | TYP | MAX       | UNIT |

|--------------------------|---------------------------|-----------------------------------------------------------------------------|------------------------|-----|-----------|------|

|                          | Output voltage            | $V_{BAT} \ge 8 \text{ V}, C_L = 1 \text{ nF}, I_{AFEFUSE} = 0 \mu A$        | 6                      | 7   | 8.65      | V    |

| V <sub>OH</sub> hiç      | high                      | $V_{BAT}$ < 8 V, $C_L$ = 1 nF, $I_{AFEFUSE}$ = 0 $\mu$ A                    | V <sub>BAT</sub> – 0.1 |     | $V_{BAT}$ | V    |

| V <sub>IH</sub>          | High-level input          |                                                                             | 1.5                    | 2.0 | 2.5       | V    |

| I <sub>AFEFUSE(PU)</sub> | Internal pullup current   | V <sub>BAT</sub> ≥ 8 V, V <sub>AFEFUSE</sub> = VSS                          |                        | 150 | 330       | nA   |

| R <sub>AFEFUSE</sub>     | Output impedance          |                                                                             | 2                      | 2.6 | 3.2       | kΩ   |

| C <sub>IN</sub>          | Input capacitance         |                                                                             |                        | 5   |           | pF   |

| t <sub>DELAY</sub>       | Fuse trip detection delay |                                                                             | 128                    |     | 256       | μs   |

| t <sub>RISE</sub>        | Fuse output rise time     | V <sub>BAT</sub> ≥ 8 V, C <sub>L</sub> = 1 nF, V <sub>OH</sub> = 0 V to 5 V |                        | 5   | 20        | μs   |

## 7.21 Internal Temperature Sensor

Typical values stated where  $T_A = 25$ °C and VCC = 14.4 V, Min/Max values stated where  $T_A = -40$ °C to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                   | PARAMETER                                       | TEST CONDITIONS                                             | MIN   | TYP   | MAX   | UNIT  |

|-------------------|-------------------------------------------------|-------------------------------------------------------------|-------|-------|-------|-------|

| V <sub>TEMP</sub> | Internal<br>temperature<br>sensor voltage drift | $V_{TEMPP}$                                                 | -1.9  | -2.0  | -2.1  |       |

|                   |                                                 | V <sub>TEMPP</sub> – V <sub>TEMPN</sub> , assured by design | 0.177 | 0.178 | 0.179 | mV/°C |

## 7.22 TS1, TS2, TS3, TS4

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| PAR                     | AMETER                            | TEST CONDITIONS                                           | MIN  | TYP  | MAX                   | UNIT   |

|-------------------------|-----------------------------------|-----------------------------------------------------------|------|------|-----------------------|--------|

| V <sub>IN</sub>         | Input voltage                     | TS1, TS2, TS3, TS4, V <sub>BIAS</sub> = V <sub>REF1</sub> | -0.2 |      | $0.8 \times V_{REF1}$ | V      |

|                         | range                             | TS1, TS2, TS3, TS4, $V_{BIAS} = V_{REG}$                  | -0.2 |      | $0.8 \times V_{REG}$  | V      |

| R <sub>NTC(PU)</sub>    | Internal pullup resistance        | TS1, TS2, TS3, TS4                                        | 14.4 | 18   | 21.6                  | kΩ     |

| R <sub>NTC(DRIFT)</sub> | Resistance drift over temperature | TS1, TS2, TS3, TS4                                        | -360 | -280 | -200                  | PPM/°C |

### 7.23 PTC, PTCEN

Typical values stated where  $T_A = 25$ °C and VCC = 14.4 V, Min/Max values stated where  $T_A = -40$ °C to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| PA                      | RAMETER                   | TEST CONDITIONS                                     | MIN | TYP | MAX  | UNIT      |

|-------------------------|---------------------------|-----------------------------------------------------|-----|-----|------|-----------|

| R <sub>PTC(TRIP)</sub>  | PTC trip resistance       |                                                     | 1.2 | 2.5 | 3.95 | $M\Omega$ |

| V <sub>PTC(TRIP)</sub>  | PTC trip voltage          | $V_{PTC(TRIP)} = V_{PTCEN} - V_{PTC}$               | 200 | 500 | 890  | mV        |

| I <sub>PTC</sub>        | Internal PTC current bias | $T_A = -40^{\circ}\text{C to } 110^{\circ}\text{C}$ | 200 | 290 | 350  | nA        |

| t <sub>PTC(DELAY)</sub> | PTC delay time            | $T_A = -40^{\circ}\text{C to } 110^{\circ}\text{C}$ | 40  | 80  | 145  | ms        |

## 7.24 Internal 1.8-V LDO

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| P                    | ARAMETER                                      | TEST CONDITIONS                                                                                | MIN    | TYP    | MAX  | UNIT |

|----------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------|--------|--------|------|------|

| V <sub>REG</sub>     | Regulator voltage                             |                                                                                                | 1.6    | 1.8    | 2.0  | V    |

| $\Delta V_{O(TEMP)}$ | Regulator output over temperature             | $\Delta V_{REG}/\Delta T_A$ , $I_{REG} = 10 \text{ mA}$                                        |        | ±0.25% |      |      |

| $\Delta V_{O(LINE)}$ | Line regulation                               | $\Delta V_{REG}/\Delta V_{BAT}$ , $V_{BAT} = 10 \text{ mA}$                                    | -0 .6% |        | 0.5% |      |

| $\Delta V_{O(LOAD)}$ | Load regulation                               | $\Delta V_{REG}/\Delta I_{REG}$ , $I_{REG}$ = 0 mA to 10 mA                                    | -1.5%  |        | 1.5% |      |

| I <sub>REG</sub>     | Regulator output current limit                | $V_{REG} = 0.9 \times V_{REG(NOM)}, V_{IN} > 2.2 V$                                            | 20     |        |      | mA   |

| I <sub>SC</sub>      | Regulator short-<br>circuit current limit     | $V_{REG} = 0 \times V_{REG(NOM)}$                                                              | 25     | 40     | 55   | mA   |

| PSRR <sub>REG</sub>  | Power supply rejection ratio                  | $\Delta V_{BAT}/\Delta V_{REG}$ , I <sub>REG</sub> = 10 mA ,V <sub>IN</sub> > 2.5 V, f = 10 Hz |        | 40     |      | dB   |

| V <sub>SLEW</sub>    | Slew rate<br>enhancement<br>voltage threshold | V <sub>REG</sub>                                                                               | 1.58   | 1.65   |      | V    |

## 7.25 High-Frequency Oscillator

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                               | PARAMETER           | TEST CONDITIONS                                                      | MIN   | TYP    | MAX  | UNIT |

|-------------------------------|---------------------|----------------------------------------------------------------------|-------|--------|------|------|

| f <sub>HFO</sub>              | Operating frequency |                                                                      |       | 16.78  |      | MHz  |

| f <sub>HFO(ERR)</sub> Frequer | Crosuppou pres      | $T_A = -20$ °C to 70°C, includes frequency drift                     | -2.5% | ±0.25% | 2.5% |      |

|                               | Frequency error     | $T_A = -40$ °C to 85°C, includes frequency drift                     | -3.5% | ±0.25% | 3.5% |      |

| t <sub>HFO(SU)</sub>          | Start-up time       | $T_A = -20$ °C to 85°C, oscillator frequency within +/-3% of nominal |       |        | 4    | ms   |

|                               |                     | oscillator frequency within +/-3% of nominal                         |       |        | 100  | μs   |

## 7.26 Low-Frequency Oscillator

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| P                      | ARAMETER                    | TEST CONDITIONS                                  | MIN   | TYP     | MAX  | UNIT |

|------------------------|-----------------------------|--------------------------------------------------|-------|---------|------|------|

| $f_{LFO}$              | Operating frequency         |                                                  |       | 262.144 |      | kHz  |

| f <sub>LFO(ERR)</sub>  | Frequency error             | $T_A = -20$ °C to 70°C, includes frequency drift | -1.5% | ±0.25%  | 1.5% |      |

|                        |                             | $T_A = -40$ °C to 85°C, includes frequency drift | -2.5  | ±0.25   | 2.5  |      |

| f <sub>LFO(FAIL)</sub> | Failure detection frequency |                                                  | 30    | 80      | 100  | kHz  |

## 7.27 Voltage Reference 1

Typical values stated where  $T_A = 25$ °C and VCC = 14.4 V, Min/Max values stated where  $T_A = -40$ °C to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| P                         | PARAMETER                        | TEST CONDITIONS                    | MIN  | TYP   | MAX  | UNIT     |

|---------------------------|----------------------------------|------------------------------------|------|-------|------|----------|

| V <sub>REF1</sub>         | Internal reference voltage       | T <sub>A</sub> = 25°C, after trim  | 1.21 | 1.215 | 1.22 | V        |

| V                         | Internal reference voltage drift | $T_A = 0$ °C to 60°C, after trim   |      | ±50   |      | PPM/°C   |

| V <sub>REF1</sub> (DRIFT) |                                  | $T_A = -40$ °C to 85°C, after trim |      | ±80   |      | PPIVI/°C |

### 7.28 Voltage Reference 2

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| F                        | PARAMETER                  | TEST CONDITIONS                    | MIN  | TYP   | MAX  | UNIT   |

|--------------------------|----------------------------|------------------------------------|------|-------|------|--------|

| V <sub>REF2</sub>        | Internal reference voltage | T <sub>A</sub> = 25°C, after trim  | 1.22 | 1.225 | 1.23 | V      |

| V                        | Internal reference         | $T_A = 0$ °C to 60°C, after trim   |      | ±50   |      | DDM/9C |

| V <sub>REF2(DRIFT)</sub> |                            | $T_A = -40$ °C to 85°C, after trim |      | ±80   |      | PPM/°C |

### 7.29 Instruction Flash

Typical values stated where  $T_A = 25$ °C and VCC = 14.4 V, Min/Max values stated where  $T_A = -40$ °C to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| P                       | ARAMETER                       | TEST CONDITIONS        | MIN  | TYP | MAX | UNIT   |

|-------------------------|--------------------------------|------------------------|------|-----|-----|--------|

|                         | Data retention                 |                        | 10   |     |     | Years  |

|                         | Flash programming write cycles |                        | 1000 |     |     | Cycles |

| t <sub>PROGWORD</sub>   | Word programming time          | $T_A = -40$ °C to 85°C |      |     | 40  | μs     |

| t <sub>MASSERASE</sub>  | Mass-erase time                | $T_A = -40$ °C to 85°C |      |     | 40  | ms     |

| t <sub>PAGEERASE</sub>  | Page-erase time                | $T_A = -40$ °C to 85°C |      |     | 40  | ms     |

| I <sub>FLASHREAD</sub>  | Flash-read current             | $T_A = -40$ °C to 85°C |      |     | 2   | mA     |

| I <sub>FLASHWRITE</sub> | Flash-write current            | $T_A = -40$ °C to 85°C |      |     | 5   | mA     |

| I <sub>FLASHERASE</sub> | Flash-erase current            | $T_A = -40$ °C to 85°C |      |     | 15  | mA     |

### 7.30 Data Flash

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

| P                       | ARAMETER                       | TEST CONDITIONS                                    | MIN   | TYP | MAX | UNIT   |

|-------------------------|--------------------------------|----------------------------------------------------|-------|-----|-----|--------|

|                         | Data retention                 |                                                    | 10    |     |     | Years  |

|                         | Flash programming write cycles |                                                    | 20000 |     |     | Cycles |

| t <sub>PROGWORD</sub>   | Word programming time          | $T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C}$ |       |     | 40  | μs     |

| t <sub>MASSERASE</sub>  | Mass-erase time                | $T_A = -40$ °C to 85°C                             |       |     | 40  | ms     |

| t <sub>PAGEERASE</sub>  | Page-erase time                | $T_A = -40$ °C to 85°C                             |       |     | 40  | ms     |

| I <sub>FLASHREAD</sub>  | Flash-read current             | $T_A = -40$ °C to 85°C                             |       |     | 1   | mA     |

| I <sub>FLASHWRITE</sub> | Flash-write current            | $T_A = -40$ °C to 85°C                             |       |     | 5   | mA     |

| I <sub>FLASHERASE</sub> | Flash-erase current            | $T_A = -40$ °C to 85°C                             |       |     | 15  | mA     |

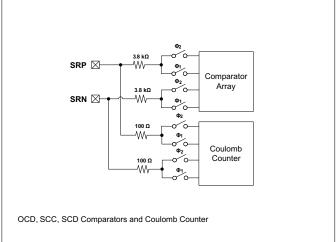

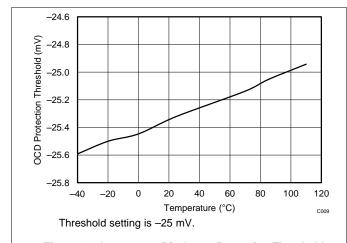

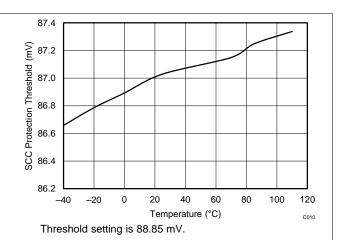

# 7.31 OCD, SCC, SCD1, SCD2 Current Protection Thresholds

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                     | PARAMETER                                           | TEST CONDITIONS                                                                               | MIN   | TYP   | MAX  | UNIT |

|---------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------|-------|-------|------|------|

| V <sub>OCD</sub>    | OCD detection threshold voltage range               | V <sub>OCD</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> , AFE PROTECTION<br>CONTROL[RSNS] = 1  | -16.6 |       | -100 | mV   |

|                     |                                                     | $V_{OCD} = V_{SRP} - V_{SRN}$ , AFE PROTECTION CONTROL[RSNS] = 0                              | -8.3  |       | -50  | IIIV |

| $\Delta V_{OCD}$    | OCD detection<br>threshold voltage<br>program step  | $V_{OCD} = V_{SRP} - V_{SRN}$ , AFE PROTECTION CONTROL[RSNS] = 1                              |       | -5.56 |      | mV   |

|                     |                                                     | V <sub>OCD</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> , AFE PROTECTION<br>CONTROL[RSNS] = 0  |       | -2.78 |      |      |

| V <sub>SCC</sub>    | SCC detection threshold voltage range               | V <sub>SCC</sub> = V <sub>SRP</sub> – V <sub>SRN</sub> , AFE PROTECTION<br>CONTROL[RSNS] = 1  | 44.4  |       | 200  | .,   |

|                     |                                                     | V <sub>SCC</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> , AFE PROTECTION<br>CONTROL[RSNS] = 0  | 22.2  |       | 100  | mV   |

| 437                 | SCC detection<br>threshold voltage<br>program step  | V <sub>SCC</sub> = V <sub>SRP</sub> – V <sub>SRN</sub> , AFE PROTECTION<br>CONTROL[RSNS] = 1  |       | 22.2  |      | mV   |

| $\Delta V_{SCC}$    |                                                     | V <sub>SCC</sub> = V <sub>SRP</sub> - V <sub>SRN</sub> , AFE PROTECTION<br>CONTROL[RSNS] = 0  |       | 11.1  |      |      |

| V <sub>SCD1</sub>   | SCD1 detection threshold voltage range              | V <sub>SCD1</sub> = V <sub>SRP</sub> – V <sub>SRN</sub> , AFE PROTECTION<br>CONTROL[RSNS] = 1 | -44.4 |       | -200 | mV   |

|                     |                                                     | V <sub>SCD1</sub> = V <sub>SRP</sub> – V <sub>SRN</sub> , AFE PROTECTION<br>CONTROL[RSNS] = 0 | -22.2 |       | -100 |      |

| $\Delta V_{SCD1}$   | SCD1 detection<br>threshold voltage<br>program step | V <sub>SCD1</sub> = V <sub>SRP</sub> – V <sub>SRN</sub> , AFE PROTECTION<br>CONTROL[RSNS] = 1 |       | -22.2 |      | mV   |

|                     |                                                     | V <sub>SCD1</sub> = V <sub>SRP</sub> – V <sub>SRN</sub> , AFE PROTECTION<br>CONTROL[RSNS] = 0 |       | -11.1 |      |      |

|                     | SCD2 detection threshold voltage range              | V <sub>SCD2</sub> = V <sub>SRP</sub> – V <sub>SRN</sub> , AFE PROTECTION<br>CONTROL[RSNS] = 1 | -44.4 |       | -200 |      |

| V <sub>SCD2</sub>   |                                                     | V <sub>SCD2</sub> = V <sub>SRP</sub> – V <sub>SRN</sub> , AFE PROTECTION<br>CONTROL[RSNS] = 0 | -22.2 |       | -100 | mV   |

| 41/                 | SCD2 detection<br>threshold voltage<br>program step | V <sub>SCD2</sub> = V <sub>SRP</sub> – V <sub>SRN</sub> , AFE PROTECTION<br>CONTROL[RSNS] = 1 |       | -22.2 |      | mV   |

| $\Delta V_{SCD2}$   |                                                     | V <sub>SCD2</sub> = V <sub>SRP</sub> – V <sub>SRN</sub> , AFE PROTECTION<br>CONTROL[RSNS] = 0 |       | -11.1 |      |      |

| V <sub>OFFSET</sub> | OCD, SCC, and SCDx offset error                     | Post-trim                                                                                     | -2.5  |       | 2.5  | mV   |

| \/                  | OCD, SCC, and SCDx                                  | No trim                                                                                       | -10%  |       | 10%  |      |

| V <sub>SCALE</sub>  | scale error                                         | Post-trim Post-trim                                                                           | -5%   |       | 5%   | 6    |

## 7.32 Timing Requirements: OCD, SCC, SCD1, SCD2 Current Protection Timing

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                   |                                             |                                    | MIN | NOM | MAX  | UNIT |

|-------------------|---------------------------------------------|------------------------------------|-----|-----|------|------|

| t <sub>OCD</sub>  | OCD detection delay time                    |                                    | 1   |     | 31   | ms   |

| $\Delta t_{OCD}$  | OCD detection<br>delay time<br>program step |                                    |     | 2   |      | ms   |

| t <sub>SCC</sub>  | SCC detection delay time                    |                                    | 0   |     | 915  | μs   |

| $\Delta t_{SCC}$  | SCC detection<br>delay time<br>program step |                                    |     | 61  |      | μs   |

| t <sub>SCD1</sub> | SCD1 detection delay time                   | AFE PROTECTION CONTROL[SCDDx2] = 0 | 0   |     | 915  |      |

|                   |                                             | AFE PROTECTION CONTROL[SCDDx2] = 1 | 0   |     | 1850 | μs   |

## Timing Requirements: OCD, SCC, SCD1, SCD2 Current Protection Timing (continued)

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                     |                                              |                                                                                                   | MIN  | NOM  | MAX | UNIT |  |

|---------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------|------|------|-----|------|--|

| $\Delta t_{SCD1}$   | SCD1 detection<br>delay time<br>program step | AFE PROTECTION CONTROL[SCDDx2] = 0                                                                |      | 61   |     |      |  |

|                     |                                              | AFE PROTECTION CONTROL[SCDDx2] = 1                                                                |      | 121  |     | μs   |  |

| t <sub>SCD2</sub>   | SCD2 detection delay time                    | AFE PROTECTION CONTROL[SCDDx2] = 0                                                                | 0    |      | 458 |      |  |

|                     |                                              | AFE PROTECTION CONTROL[SCDDx2] = 1                                                                | 0    |      | 915 | μs   |  |

| Δt <sub>SCD2</sub>  | SCD2 detection<br>delay time<br>program step | AFE PROTECTION CONTROL[SCDDx2] = 0                                                                |      | 30.5 |     |      |  |

|                     |                                              | AFE PROTECTION CONTROL[SCDDx2] = 1                                                                |      | 61   |     | μs   |  |

| t <sub>DETECT</sub> | Current fault detect time                    | $V_{SRP} - V_{SRN} = V_T - 3$ mV for OCD, SCD1, and SC2, $V_{SRP} - V_{SRN} = V_T + 3$ mV for SCC |      |      | 160 | μs   |  |

| t <sub>ACC</sub>    | Current fault delay time accuracy            | Max delay setting                                                                                 | -10% |      | 10% |      |  |

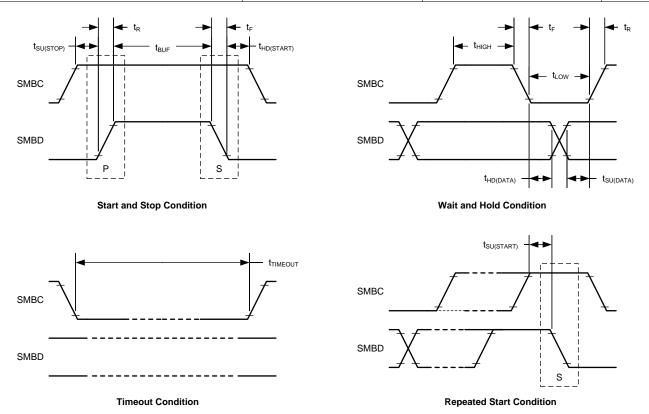

## 7.33 Timing Requirements: SMBus

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                        |                                         |                                        | MIN | NOM  | MAX  | UNIT |

|------------------------|-----------------------------------------|----------------------------------------|-----|------|------|------|

| f <sub>SMB</sub>       | SMBus operating frequency               | SLAVE mode, SMBC 50% duty cycle        | 10  |      | 100  | kHz  |

| f <sub>MAS</sub>       | SMBus master clock frequency            | MASTER mode, no clock low slave extend |     | 51.2 |      | kHz  |

| t <sub>BUF</sub>       | Bus free time between start and stop    |                                        | 4.7 |      |      | μs   |

| t <sub>HD(START)</sub> | Hold time after (repeated) start        |                                        | 4.0 |      |      | μs   |

| t <sub>SU(START)</sub> | Repeated start setup time               |                                        | 4.7 |      |      | μs   |

| t <sub>SU(STOP)</sub>  | Stop setup time                         |                                        | 4.0 |      |      | μs   |

| t <sub>HD(DATA)</sub>  | Data hold time                          |                                        | 300 |      |      | ns   |

| t <sub>SU(DATA)</sub>  | Data setup time                         |                                        | 250 |      |      | ns   |

| t <sub>TIMEOUT</sub>   | Error signal detect time                |                                        | 25  |      | 35   | ms   |

| $t_{LOW}$              | Clock low period                        |                                        | 4.7 |      |      | μs   |

| t <sub>HIGH</sub>      | Clock high period                       |                                        | 4.0 |      | 50   | μs   |

| t <sub>R</sub>         | Clock rise time                         | 10% to 90%                             |     |      | 1000 | ns   |

| t <sub>F</sub>         | Clock fall time                         | 90% to 10%                             |     |      | 300  | ns   |

| t <sub>LOW(SEXT)</sub> | Cumulative clock low slave extend time  |                                        |     |      | 25   | ms   |

| t <sub>LOW(MEXT)</sub> | Cumulative clock low master extend time |                                        |     |      | 10   | ms   |

## 7.34 Timing Requirements: SMBus XL

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                        |                                      |            | MIN | NOM MAX | UNIT |

|------------------------|--------------------------------------|------------|-----|---------|------|

| f <sub>SMBXL</sub>     | SMBus XL operating frequency         | SLAVE mode | 40  | 400     | kHz  |

| t <sub>BUF</sub>       | Bus free time between start and stop |            | 4.7 |         | μs   |

| t <sub>HD(START)</sub> | Hold time after (repeated) start     |            | 4.0 |         | μs   |

# Timing Requirements: SMBus XL (continued)

Typical values stated where  $T_A = 25^{\circ}C$  and VCC = 14.4 V, Min/Max values stated where  $T_A = -40^{\circ}C$  to 85°C and VCC = 2.2 V to 26 V (unless otherwise noted)

|                        |                           | MIN    | NOM MAX | UNIT |

|------------------------|---------------------------|--------|---------|------|

|                        |                           | 191114 | HOM MAX | Oldi |

| t <sub>SU(START)</sub> | Repeated start setup time | 4.7    |         | μs   |

| t <sub>SU(STOP)</sub>  | Stop setup time           | 4.0    |         | μs   |

| t <sub>TIMEOUT</sub>   | Error signal detect time  | 5      | 20      | ms   |

| $t_{LOW}$              | Clock low period          |        | 20      | μs   |

| t <sub>HIGH</sub>      | Clock high period         |        | 20      | μs   |

Figure 4. SMBus Timing Diagram

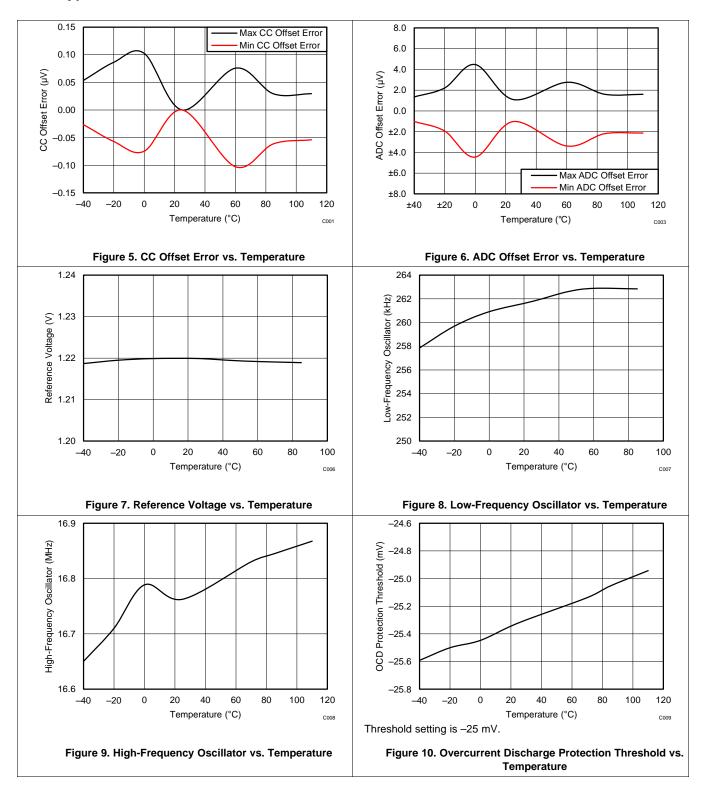

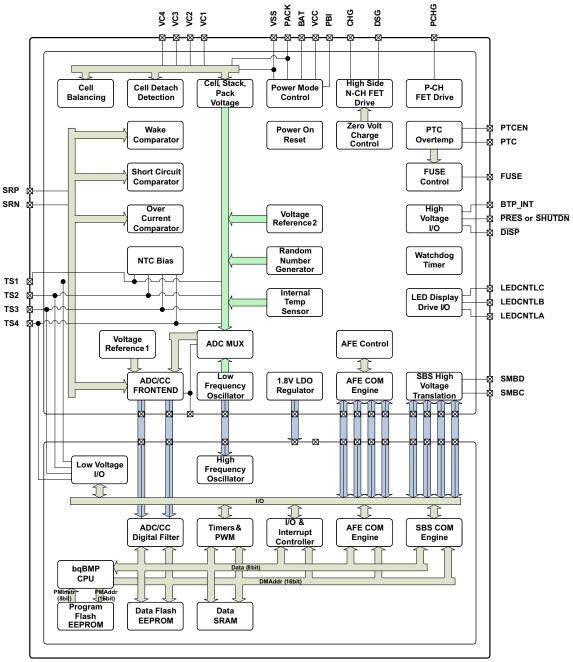

## 7.35 Typical Characteristics

## TEXAS INSTRUMENTS

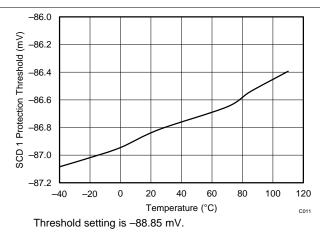

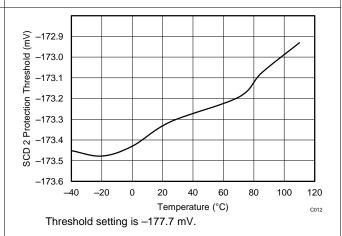

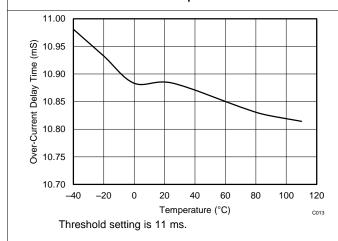

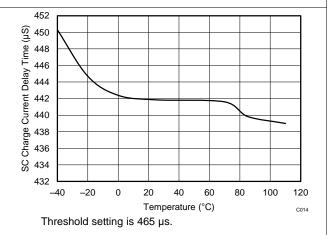

## **Typical Characteristics (continued)**

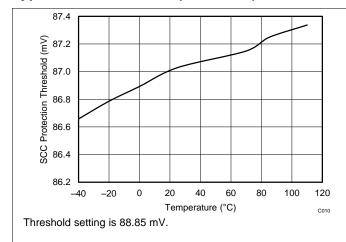

Figure 11. Short Circuit Charge Protection Threshold vs.

Temperature

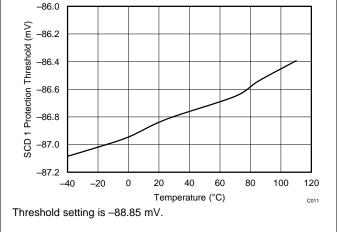

Figure 12. Short Circuit Discharge 1 Protection Threshold vs. Temperature

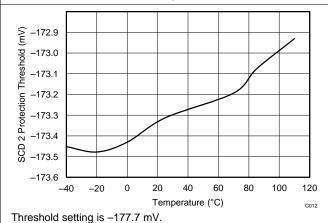

Figure 13. Short Circuit Discharge 2 Protection Threshold vs. Temperature

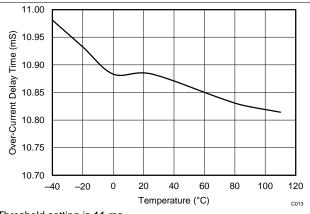

Threshold setting is 11 ms.

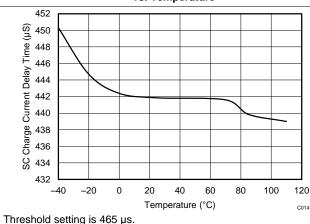

Figure 15. Short Circuit Charge Current Delay Time vs. Temperature

Figure 14. Overcurrent Delay Time vs. Temperature

Threshold setting is 465 µs (including internal delay).

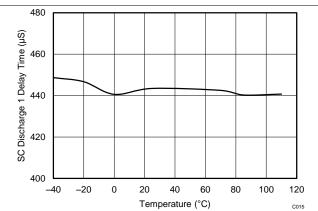

Figure 16. Short Circuit Discharge 1 Delay Time vs. Temperature

## **Typical Characteristics (continued)**

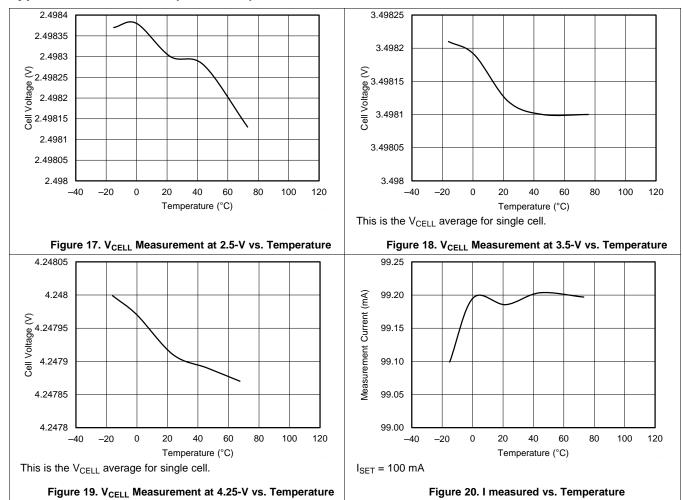

## 8 Detailed Description

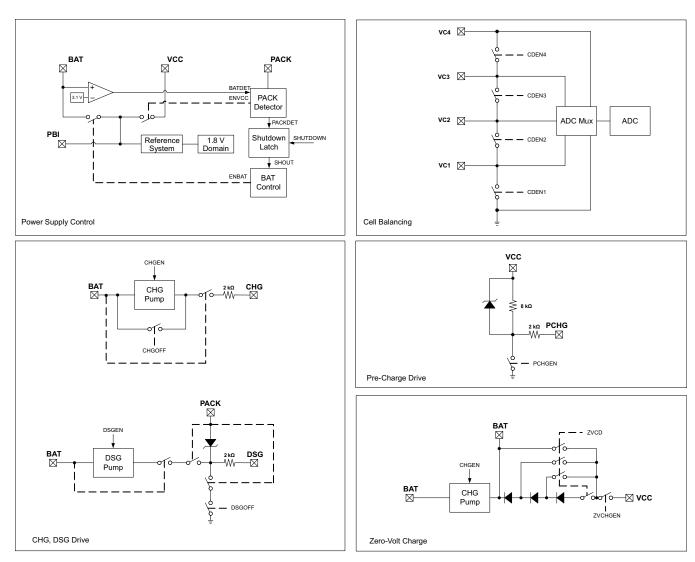

#### 8.1 Overview

The bq40z50-R2 device, incorporating patented Impedance Track™ technology, provides cell balancing while charging or at rest. This fully integrated, single-chip, pack-based solution, including a diagnostic lifetime data monitor and black box recorder, provides a rich array of features for gas gauging, protection, and authentication for 1-series, 2-series, 3-series, and 4-series cell Li-lon and Li-Polymer battery packs.

## 8.2 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

## 8.3 Feature Description

### 8.3.1 Primary (1st Level) Safety Features

The bq40z50-R2 supports a wide range of battery and system protection features that can easily be configured. See the *bq40z50-R2 Technical Reference Manual* (SLUUBK0) for detailed descriptions of each protection function.

The primary safety features include:

- Cell Overvoltage Protection

- Cell Undervoltage Protection

- Cell Undervoltage Protection Compensated

- · Overcurrent in Charge Protection

- Overcurrent in Discharge Protection

- · Overload in Discharge Protection

- · Short Circuit in Charge Protection

- Short Circuit in Discharge Protection

- Overtemperature in Charge Protection

- Overtemperature in Discharge Protection

- Undertemperature in Charge Protection

- · Undertemperature in Discharge Protection

- Overtemperature FET protection

- Precharge Timeout Protection

- Host Watchdog Timeout Protection

- Fast Charge Timeout Protection

- · Overcharge Protection

- Overcharging Voltage Protection

- Overcharging Current Protection

- Over Precharge Current Protection

### 8.3.2 Secondary (2nd Level) Safety Features

The secondary safety features of the bq40z50-R2 can be used to indicate more serious faults via the FUSE pin. This pin can be used to blow an in-line fuse to permanently disable the battery pack from charging or discharging. See the bq40z50-R2 Technical Reference Manual (SLUUBK0) for detailed descriptions of each protection function.

The secondary safety features provide protection against:

- Safety Overvoltage Permanent Failure

- Safety Undervoltage Permanent Failure

- Safety Overtemperature Permanent Failure

- Safety FET Overtemperature Permanent Failure

- Qmax Imbalance Permanent Failure

- Impedance Imbalance Permanent Failure

- Capacity Degradation Permanent Failure

- Cell Balancing Permanent Failure

- Fuse Failure Permanent Failure

- PTC Permanent Failure

- Voltage Imbalance At Rest Permanent Failure

- Voltage Imbalance Active Permanent Failure

- Charge FET Permanent Failure

- Discharge FET Permanent Failure

- AFE Register Permanent Failure

- AFE Communication Permanent Failure

### **Feature Description (continued)**

- Second Level Protector Permanent Failure

- Instruction Flash Checksum Permanent Failure

- Open Cell Connection Permanent Failure

- · Data Flash Permanent Failure

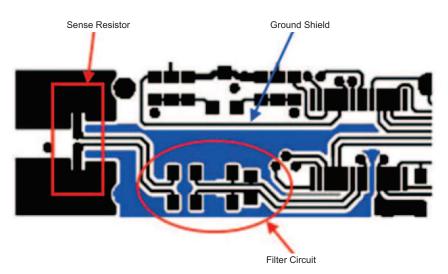

- Open Thermistor Permanent Failure