## Zero-crossover Amplifiers: Features and Benefits

## Errol Leon, Richard Barthel, Tamara Alani

# **Texas Instruments**

## 1 Introduction

Zero-crossover amplifiers employ a unique topology which eliminates the error induced by the crossover region that standard rail-to-rail amplifiers have. TI's zero-crossover topology assures high linearity across the entire common-mode voltage range and lowest distortion for precision and general applications. This tech note will explain the differences between standard rail-to-rail input and zero-crossover amplifiers.

### Traditional rail-to-rail CMOS input

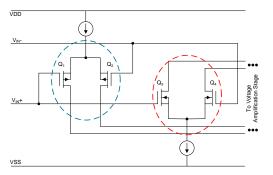

A traditional rail-to-rail input CMOS architecture has two differential pairs. Figure 1 highlights two differential pairs; one PMOS transistor pair (blue) and one NMOS transistor pair (red). PMOS transistors can operate in common-mode input voltages from VSS to (VDD-1.8V) and NMOS transistors can operate in common-mode input voltages from (VDD-1.8V) to VDD. The two input transistor pairs will have independent and uncorrelated input offset voltages, temperature coefficients and noise.

Figure 1. Simplified PMOS / NMOS Differential Pair

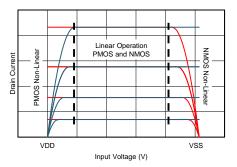

During the transition from the PMOS pair to the NMOS pair, and vice versa, there is a crossover region at  $\approx$ 1.8V below the positive rail where both inputs are conducting (see Figure 2). Within this region, the DC input offset voltage can change – this is a source of distortion known as *input crossover distortion*. This offset error can be simulated using the TINA-TI SPICE tool (ti.com/tool/tina-ti).

Figure 2. Transistor IV Curves

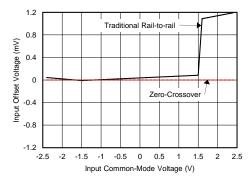

Figure 3. Simulated Crossover Performance

Figure 3 shows the simulated results of applying a [-2.4V, 2.4V] DC sweep to a traditional rail-to-rail CMOS input, buffer-configured op amp. The graph shows the *input offset voltage* abruptly shifts when the common-mode voltage is within the crossover region. If this error source is beyond the error budget, a zero-crossover amplifier will be needed.

### How zero-crossover works

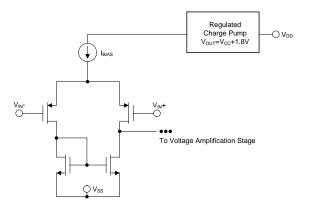

Zero-crossover topology uses a internal voltage charge pump to achieve linear operation with input voltages up to the rail with a single input transistor pair (PMOS or NMOS). This use of a single transistor pair allows true rail-to-rail operation without distortion over the entire input common-mode range since there is no crossover region. Zero-crossover amplifiers such as the OPA388 include an internal voltage charge pump. The charge pump boosts the input stage voltage ≈1.8V

1

above VDD. This is enough to overcome the nonlinearity that occurs when the transistor enters triode operation at  $V_{DS}$  < 1.8V. Figure 4 shows a simplified representation of the charge pump topology used in zero-crossover amplifiers.

Figure 4. Simplified Zero-crossover Charge Pump Topology

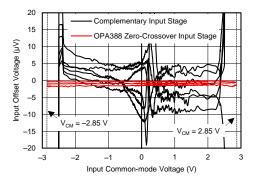

Figure 3 also shows the simulated results of applying a [-2.4V, 2.4V] DC sweep on a buffer-configured OPA388. The input offset voltage trace in the graph shows no abrupt shift with input common-mode change because there is no crossover region. Figure 5 below contrasts the measured performance between a complementary rail-to-rail input and zero-crossover amplifier. Note the large variance in offset voltage across the input common-mode voltage.

Figure 5. Measured Crossover Performance

#### Zero-crossover vs. rail-to-rail CMOS results

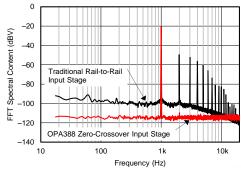

A zero-crossover and a standard rail-to-rail CMOS amplifier were used in identical, unity-gain buffer configurations. These amplifiers were both fed a pure sine wave with an amplitude of 2V ( $4V_{PP}$ ). The outputs of these circuits were captured and the FFT was computed. Figure 6 illustrates the output voltage spectrum for the OPA388 (red) and a typical CMOS

rail-to-rail amplifier (black). The output of the zerocrossover amplifier has very few spurs and harmonics compared to the typical rail-to-rail CMOS amplifier. This is the effect of eliminating the crossover region with zero-crossover topology.

Figure 6. Buffer FFT Spectrum

#### Again, why zero-crossover?

Traditional rail-to-rail input CMOS op amps use two parallel differential input transistor pairs. When the common-mode is in the transition region (deadband), there is an abrupt shift in the input offset voltage which results in output voltage error and distortion. Zerocrossover op amps vastly reduce any changes in input offset voltage across the entire input common-mode range.

#### **Additional Resources**

Table 1 highlights some of TI's zero-crossover amplifiers. For a full list, see our parametric search tool results by visiting: ti.com/opamps.

#### **Table 1. Alternative Device Recommendations**

| Device   | Optimized Parameters                                                                                                                                   |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPA388   | Zero-drift, V <sub>os(max)</sub> : 5μV, dV <sub>os</sub> /dT <sub>(max)</sub> : 0.05μV/°C,<br>CMRR: 138dB, GBW: 10MHz, Noise: 7nV/√Hz                  |

| OPA320   | V <sub>os(max)</sub> : 150µV, CMRR: 114dB, I <sub>B(max)</sub> : 0.9pA,<br>1.8V <vs<5.5v, 20mhz,="" 7nv="" gbw:="" noise:="" td="" √hz<=""></vs<5.5v,> |

| OPA2325  | V <sub>os(max)</sub> : 150µV, CMRR: 114dB, I <sub>B(max)</sub> : 10pA,<br>GBW: 10MHz, Noise: 9nV/√Hz                                                   |

| OPA365   | V <sub>os(max)</sub> : 200µV, CMRR: 120dB, GBW: 50MHz,<br>Noise: 4.5nV/√Hz, Slew rate: 25V/µs, 1.8V <v<sub>S&lt;5.5V</v<sub>                           |

| OPA322   | V <sub>os(max)</sub> : 2mV, CMRR: 100dB, GBW: 20MHz,<br>Noise: 8.5nV/√ <del>Hz</del> , Slew Rate: 10V/µs, 1.8V <v<sub>S&lt;5.5V</v<sub>                |

| OPA363/4 | V <sub>os(max)</sub> : 2.5mV, CMRR: 90dB, GBW: 7MHz,<br>Noise: 17nV/√Hz, I <sub>B(typ</sub> : 1pA, 1.8V <v<sub>S&lt;5.5V</v<sub>                       |

| OPA369   | V <sub>os(max)</sub> : 750μV, CMRR: 114dB, GBW: 12kHz,<br>I <sub>B(typ)</sub> : 10pA, 1.8V <v<sub>S&lt;5.5V</v<sub>                                    |

| LMV951   | V <sub>os(max)</sub> : 2.8mV, CMRR: 85dB, GBW: 2.8MHz,<br>Noise: 25nV/√Hz, Slew Rate: 1.4V/µs, 0.9V <v<sub>S&lt;3V</v<sub>                             |

#### **Table 2. Related Documentation**

| SBOA182 Zero-drift Amplifiers: Features and Benefits |

|------------------------------------------------------|

|------------------------------------------------------|

www.ti.com

## 1.1 Trademarks

3

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated