Application Report SLVA889-May 2017

# Improving Boost Converter Reliability Using the TPS61178x Hiccup Mode Short Protection

Yangwei Yu

APP-BMC-CCS

1

#### ABSTRACT

This application note is provides guidance on handling the output short protection using TPS61178x devices. With a brief introduction to the output short protection functionality of the TPS61178x, a user guide of how to select the external components is presented to show a desired methods to safeguard a boost converter from short circuits.

#### Contents

|   | Introduction                              |   |

|---|-------------------------------------------|---|

| 2 | TPS61178x Hiccup Mode Protection          | 2 |

| 3 | External Components Selection             | 4 |

| 4 | Additional Capacitor Between Gate and GND | 5 |

| 5 | Summary                                   | 7 |

| 6 | References                                | 7 |

#### List of Figures

| 1 | TPS61178x Application Circuit with External P-FET                     | 2 |

|---|-----------------------------------------------------------------------|---|

| 2 | TPS61178x Hiccup Mode Protection Timing Diagram                       | 3 |

| 3 | CSD25404Q3 SOA                                                        | 5 |

| 4 | Additional Capacitor from Gate to GND to Improve the Short Protection | 5 |

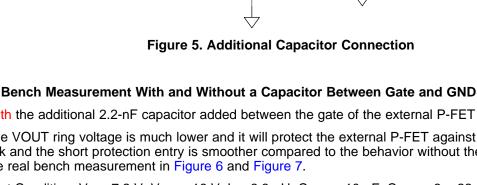

| 5 | Additional Capacitor Connection                                       | 6 |

| 6 | Short Entry With Additional Capacitor                                 | 6 |

| 7 | Short Entry Without Additional Capacitor                              | 6 |

|   |                                                                       |   |

#### Trademarks

All trademarks are the property of their respective owners.

2

#### 1 Introduction

The traditional boost converter is particularly susceptible to output short protection due to the DC path from the input to output. Usually an additional load switch is required to achieve the output short protection but it will make the circuitry more complicated and also consume more overall size and cost.

#### 2 TPS61178x Hiccup Mode Protection

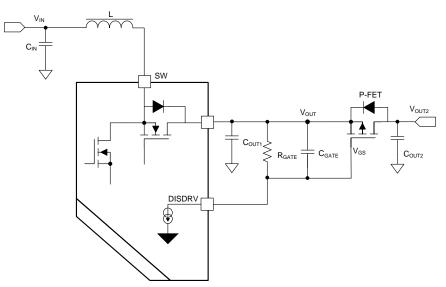

The TPS61178x integrates the hiccup mode short protection via an external P-FET as shown in Figure 1. As long as the output short condition is detected (the inductor current exceeds the short current threshold, typically 20 A or the output voltage drops below the output short threshold, typically 30% of the normal voltage), the external P-FET is turned off by disabling the internal current source sinking from the DIRDRV pin to GND.

Figure 1. TPS61178x Application Circuit with External P-FET

The device is in sleep mode once it enters into the hiccup mode. At the end of the sleep time, a restart attempt is initiated by ramping up the output voltage. If the output short condition persists, the device cannot start up successfully and enters into the sleep mode again as long as the inductor current triggers the short protection threshold, this process will be repeated during the short steady-state operation. Thus, the device is in a cycle of short burst for the start up (the time is determined by the inductor current ramping up slew rate to reach the short protection threshold) and followed by an off time (typically 90 ms) in sleep mode for the continuous short status. The off time reduces the average overall load current and also lowers the power loss to cool down the system when the output short happens.

Figure 2. TPS61178x Hiccup Mode Protection Timing Diagram

3

# 3 External Components Selection

This section discusses the gate-source resistor and capacitor, and the external P-FET specification.

# 3.1 Gate-Source Resistor and Capacitor

The TPS61178x achieves the hiccup mode protection by turning off the external P-FET. The external P-FET, gate –source resistor ( $R_{GATE}$ ) and capacitor ( $C_{GATE}$ ) are the key components to achieve the robust short protection function. When the short current threshold triggers, the current source from the DISDRV pin to GND is disabled. The gate voltage ( $C_{GATE}$ ) of the external P-FET is discharged to turn off via  $R_{GATE}$  connecting between the source and gate of the external P-FET.

R<sub>GATE</sub> is determined by the gate driving voltage of the P-FET at normal operation (see Equation 1).

$$R_{GATE} = \frac{V_{GATE}}{I_{GATE}}$$

where

- V<sub>GATE</sub> is the driving voltage of the external P-FET

- $I_{GATE}$  is the gate sinking current, typically 55 µA of TPS61178x, specified in TPS61178x data sheet (SLVSDA7). For instance,  $V_{GATE} = 5 V$  (refer to the external P-FET data sheet), then  $R_{GATE} = 90.9 k\Omega$  (1)

For the C<sub>GATE</sub>, it depends on the turn-on timing of the external P-FET (related to the startup inrush current).

$$C_{GATE\_ALL} = \frac{I_{GATE} \times T_{FET\_ON}}{V_{GATE} \quad TH}$$

where

- V<sub>GATE\_TH</sub> is the threshold voltage of the external P-FET

- $T_{FET_{ON}}$  is the turn-on time of the external P-FET during startup. For instance  $V_{GATE_{TH}} = -1 \text{ V}$ ,  $T_{FET_{ON}} = 0.5 \text{ ms}$ , then get the  $C_{GATE_{ALL}} = 27.5 \text{ nF}$ . (2)

**NOTE:** C<sub>GATE\_ALL</sub> is the total capacitor of the external gate capacitor and the FET self-gate capacitance.

$$C_{GATE} = C_{GATE_ALL} - C_{GATE_FET}$$

where

4

• C<sub>GATE</sub> is the external capacitance connecting between the source and gate of FET (3)

With total  $C_{GATE\_ALL} = 27.5 \text{ nF}$ , if the  $C_{GATE\_FET} = 1.6 \text{ nF}$  (available from the MOSFET data sheet, SLPS570), a 25-nF external capacitor is required. Choose the closet rating 22-nF capacitor in the real application.

# 3.2 External P-FET Specification

For the external P-FET, the voltage and current have a straightforward calculation:

$V_{DS} = V_{OUT}$ , while  $I_{DS_DC} = I_{OUT}$

**NOTE:** Voltage stress happens when  $V_{OUT2}$  (in Figure 1) is shorted but the  $V_{OUT}$  voltage still keeps the normal voltage.

However, the most critical specification of the external FET is the safe operation area (SOA). The heat generated during short protection:

$$Q_{GATE} = \frac{1}{2} \times V_{OUT} \times I_{SHORT} \times T_{SHORT}$$

(4)

For instance,  $V_{OUT} = 16$  V,  $I_{SHORT} = 20$  A,  $T_{SHORT} = 30$  us. The  $Q_{GATE} = 4.8$  mJ, the SOA should have enough margin to safeguard the device against damage caused by overstress.

Based on the aforementioned calculation, for instance the 16 V<sub>OUT</sub> / 3 A I<sub>OUT</sub> application case, the key specification of the external P-FET is:  $V_{DS} > 16$  V,  $I_{DS_DC} > 2$  A, SOA > 4.8 mJ.

www.ti.com

#### www.ti.com

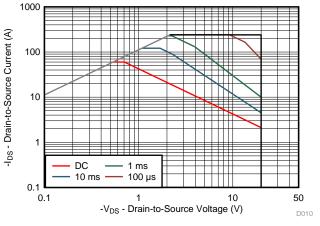

TI's low  $R_{DS(on)}$  P-FET - CSD25404Q3 is selected in the TPS61178x EVM, of which the  $V_{DS_MAX}$  is -20 V,  $I_{DS_MAX}$  is 18 A, and the SOA is around 14 mJ (reference the 100-µs curve in Figure 3).

Figure 3. CSD25404Q3 SOA

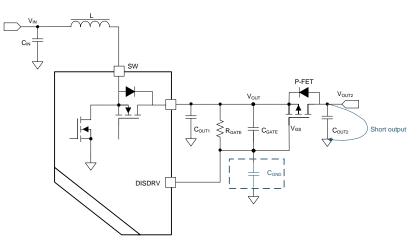

## 4 Additional Capacitor Between Gate and GND

For the TPS61178x, when the short protection triggers, the internal current source sinking from the DISDRV pin to GND is disabled to turn off the external P-FET. However, as the  $V_{OUT}$  will ring as long the external P-FET turns off, the additional capacitor from gate (of the external P-FET) to GND could lower the ring amplitude of the voltage at the VOUT pin and avoid the oscillation when entering into the short protection.

Figure 4. Additional Capacitor from Gate to GND to Improve the Short Protection

5

With the additional 2.2-nF capacitor added between the gate of the external P-FET to GND.

The VOUT ring voltage is much lower and it will protect the external P-FET against the voltage overstress risk and the short protection entry is smoother compared to the behavior without the capacitor, proven by the real bench measurement in Figure 6 and Figure 7.

Test Condition:  $V_{IN} = 7.2 \text{ V}, V_{OUT} = 16 \text{ V}, L = 3.3 \mu\text{H}, C_{OUT1} = 10 \mu\text{F}, C_{OUT2} = 3 \times 22 \mu\text{F}$ ,  $C_{GND} = 2.2 \text{ nF}$ short output. The maximum current limit of the power supply is set to 15 A.

# 8

Figure 6. Short Entry With Additional Capacitor

9w:20.0M 9w:20.0M 9w:20.0M

Short output

#### 4.1 Gate-GND Capacitor Selection

During the short protection, the VOUT maximum voltage should not exceed the VOUT boost normal operating voltage to avoid the overstress issue.

The capacitor from the gate to GND could lower the VOUT voltage during short protection.

V<sub>OUT CLAMP</sub> is defined as the maximum voltage of the VOUT pin during short protection transition. V<sub>GATE ON</sub> is the gate voltage to turn on the external P-FET to support the inductor short current flowing through the external P-FET (the positive voltage from source to gate the FET).

$$(V_{OUT\_CIAMP} - V_{GATE\_ON}) \times C_{GATE} = V_{GATE\_ON} \times C_{GND}$$

(5)

For instance, V<sub>OUT CLAMP</sub> = 20 V, C<sub>GATE</sub> = 22 nF, V<sub>GATE ON</sub> = 2 V (the source voltage reference to the gate voltage).

$C_{\text{GATE}}$

CGND

To attain  $C_{GND}$  = 2.5 nF, select the 2.2 nF capacitor in the real application.

Vout

$C_{\text{OUT1}}$

$$V_{\text{OUT CIAMP}} - V_{\text{GATE ON}} \times C_{\text{GATE}} = V_{\text{GATE ON}} \times C_{\text{GND}}$$

(5)

Gate

www.ti.com

6

4.1.1

www.ti.com

#### 5 Summary

The TPS61178x uses hiccup mode protection to safeguard the device against an output short condition by reducing the power dissipation and lowering case temperature.

This application note delivers a guidance of selecting the gate resistor and capacitors to optimize the short protection behavior. The bench measurement based on the TPS61178EVM-792 is enclosed and proves the improved performance with the application guidance proposed in this application note.

## 6 References

- TPS61178x data sheet (SLVSDA7)

- CSD25404Q3 data sheet (SLPS570)

7

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated