# Digital RF Power Control for Power Amplifier Protection in Wireless Base-Stations

#### ABSTRACT

In a wireless base-station (BS), when the output power of an RF power amplifier (PA) exceeds predefined limits, the antenna and other sensitive electronic components can be permanently damaged. This can lead to frequent and costly maintenance of BS equipment. Also very high PA output power causes neighboring BS cells to experience higher than normal interference. This is especially critical where code-division multiple access is used (that is, in W-CDMA systems). Multiple BS share the same frequency spectrum so signals from one BS appear as noise to another BS. Thus power control is important to keep the in-band noise level low and achieve reasonable carrier to noise ratio. Power control is also important in systems using frequency division multiple access to achieve a high frequency reuse factor.

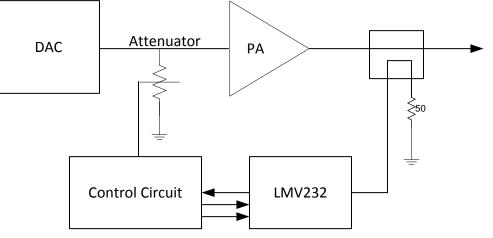

In the SNWA003, a technique to control the RF power is introduced. It uses a directional coupler to sense the RF power, an LMV232 RF power detector to compute the mean square power, a control circuit and an attenuator to adjust the RF power. Figure 1 shows this approach.

Figure 1. RF Power Control with LMV232

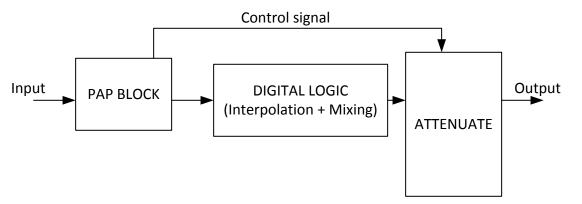

A digital based alternative to SNWA003 is discussed here and the block diagram is shown in Figure 2. It is referred to as Power Amplifier Protection (PAP). The PAP block monitors continuously the running average of the input signal magnitude and compares it to a programmable threshold. If the running average exceeds the threshold, a control signal from the PAP block to an attenuator is triggered which causes the output power to reduce gradually to zero. Digital to analog converters like DAC38J8x and DAC38RF8x devices integrate this approach so that RF power control can be achieved with no extra external components.

1

# 1 State Transitions of PAP Block

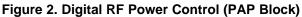

Figure 3. State Diagram of PAP block

# 1.1 NORMAL State

2

This is the normal operating condition for the PAP block. Input and output data of PAP block are the same.

## 1.2 ATTENUATE State

When the PAP block detects an error condition (or when the average power exceeds a pre-defined threshold) it sets the pap\_trig signal to '1' causing a state transition from NORMAL operation to ATTENUATE. In the ATTENUTATE state the data path gain (*pap\_gain*) is scaled from 1 down to 0 by an attenuator with programmable step size. Each clock cycle (16 samples) the gain is stepped down until the *pap\_gain* is 0.

### 1.3 WAIT State

After the  $pap\_trig$  is 0, the state machine transitions to the WAIT state. Here a programmable counter counts down to allow the condition causing the  $pap\_trig$  to be asserted to be fixed. The number of clock cycles the counter counts is programmable. Once the counter equals zero and  $pap\_trig = '0'$ , the state machine transitions to the GAIN state. Figure 4 shows the effect of different wait times when transitioning to the GAIN state. If the wait counter equals 0 but  $pap\_trig$  still equals '1' then the state machine stays in the WAIT state until  $pap\_trig = '0'$ .

Figure 4. PAP output showing effect of wait time on ATTENUATE to GAIN transition

### 1.4 GAIN State

The attenuation that was applied in the ATTENUATE state is reversed to restore full signal power. In this state, the data path gain is ramped up from 0 to 1.

Table 1 summarizes the configurable parameters of the PAP block.

| Table 1. C | Configurable | Parameters |

|------------|--------------|------------|

|------------|--------------|------------|

| PARAMETER | DESCRIPTION                                                                              | ACRONYM           |

|-----------|------------------------------------------------------------------------------------------|-------------------|

| Threshold | Sets the average power threshold                                                         | mem_threshold     |

| Step size | Step size of the attenuator and gain blocks                                              | mem_pap_gain_step |

| Wait      | Minimum clock cycles to wait between attenuate and gain state                            | mem_pap_wait      |

| Length    | Number of samples used to compute the average power. Available options are 32, 64 or 128 | mem_length        |

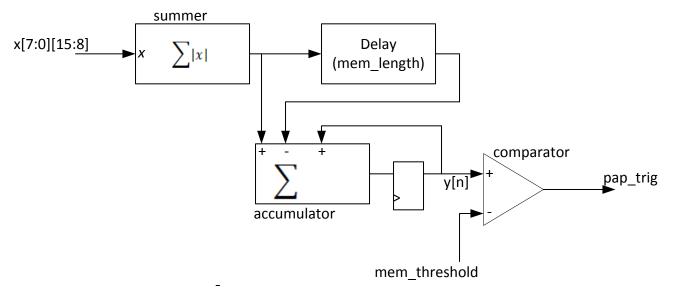

#### 2 Implementation and IIR Filter Model

A section of the PAP block is shown in Figure 5. The input to the PAP block consists of the MSB byte (or bits 15:8) of eight consecutive 16-bit samples (this is denoted as x[7:0][15:8] in Figure 5). The absolute value of the input data is found before summing. The summer output is fed into the positive input of an accumulator and a delayed version of the summer output is also fed to the accumulators negative input. The summers output is delayed by an amount specified by the parameter *mem\_length*. The other positive input to the accumulator comes from the previous accumulator output (y[n-1]). A comparator compares the current accumulator output value (y[n]) with the parameter *mem\_threshold* and generates a *pap\_trig* signal if y[n] is greater than *mem\_threshold*.

Consequently, the output of the accumulator in PAP block can be modeled by the following IIR filter Equation 1.

$$y[n] = y[n-1] + \left(x[n] - x\right) \frac{\left[\left(\frac{n - \text{mem\_length}}{8}\right)\right]}{\left(\frac{\text{mem\_length}}{16}\right)}$$

(1)

Where:

4

$y[n] \rightarrow$  output of PAP accumulator block (*mem\_threshold* is compared to y[n]).

$x[n] \rightarrow$  sum of absolute values of MSB byte of 8 consecutive 16-bits input.

*mem\_length*  $\rightarrow$  Length of moving average filter.

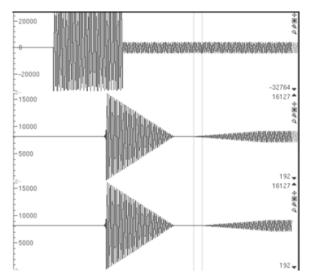

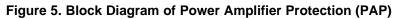

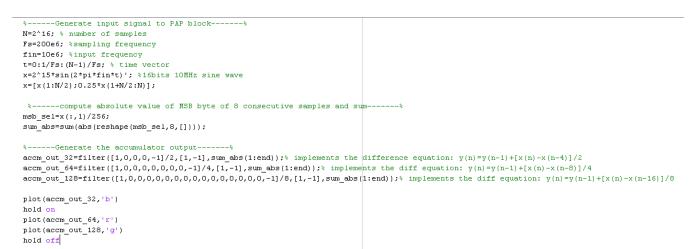

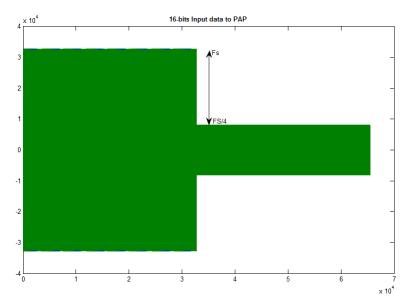

An example script written in MATLAB to compute the output of the accumulator is given in Figure 6. The input (x[n]) is 16-bits sine wave with two amplitude values that differ by  $\frac{1}{4}$  (Figure 7). The output of the accumulator (y[n]) for this input for the three different *mem\_length* settings (32, 64 and 128) is shown in Figure 8.

Figure 7. Two-Level Sine Wave Input to PAP Block

Figure 8. Accumulator Output of 2-Level Sine Wave Input

Step Size and Response Time

www.ti.com

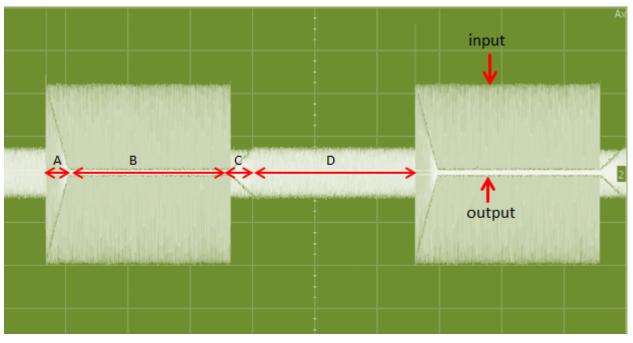

Based on the 2-level sine wave input to the PAP block in Figure 7 and the resulting accumulator output in Figure 8, when the parameter *mem\_threshold* is set to 1000, the final output of the PAP block is as shown in Figure 9. The state machine transitions through all the four states: ATTENUATE (A), WAIT (B), GAIN (C) and NORMAL (D).

Figure 9. Output of PAP Block for a 2-Level Sine Wave Input and mem\_threshold = 1000.

### 3 Step Size and Response Time

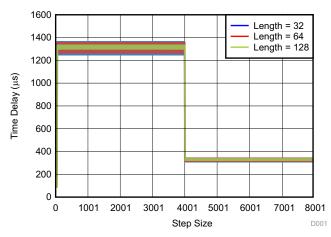

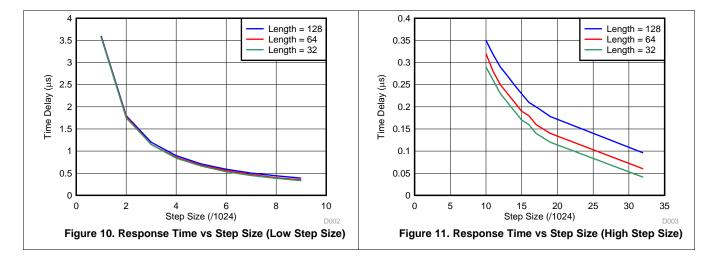

The response time is defined as the time the PAP state machine stays in either the ATTENUATE state (state A in Figure 9) or GAIN state (state C in Figure 9).

The response time is inversely proportional to the step size (*mem\_pap\_gain\_step*) and at high step size, it is also directly proportional to the length parameter (*mem\_length*). This is illustrated in Figure 10 and Figure 11.

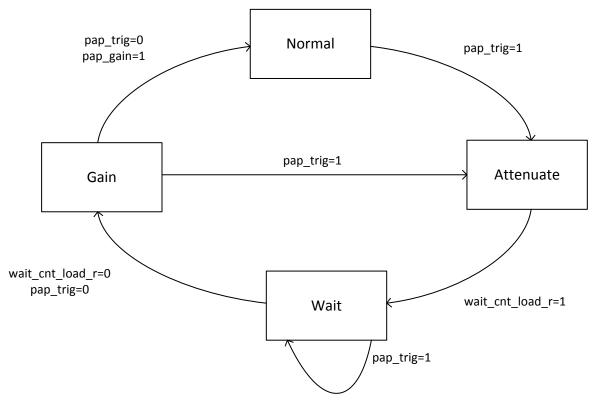

#### 4 Power Amplifier Protection in DAC38RF8x Devices

The DAC38RF8xx is a family of 9 GSPS digital to analog converters that integrate the PAP block discussed in the previous sections. This enables system designers to easily control the RF output power below a specified threshold without the need for extra external components or data processing. The DAC38RF8x EVM (Evaluation module) and the accompanying graphical user interface (GUI) can be used to test the functionality of the DAC and all its features including the PAP. The user interface of the PAP block is shown in Figure 12 and Table 2 describes the functions of all the controls and indicators on the interface.

| uick Start                                                                                                                                                                                              | DAC38RF8x    | LMK04828      | Low Level V               |            |                                    |                                                                     | DAC ALA                                       | ARMS USB Status 🔵 🗌                                                                     | 参 Recor |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|---------------------------|------------|------------------------------------|---------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------|---------|

| Overview                                                                                                                                                                                                | Clocking     | SERDES and La | ane Configuration         | JESD Block | Digital(DAC A                      | ) Digital(D                                                         | AC B) PAP                                     | Alarm Monitoring                                                                        |         |

| Pap_trig = 0 and<br>pap_geain = 1<br>GAIN<br>Pap_trig = 1<br>GAIN<br>Pap_trig = 1<br>Attenuation of output<br>Pap_trig = 1<br>ATTENUATE<br>Valt_<br>Load the wait counter<br>when pap_gain = 0<br>DAC A |              |               |                           |            |                                    |                                                                     |                                               |                                                                                         |         |

| Enable Pa<br>Step size<br>Lengtl<br>Thresho<br>Wai                                                                                                                                                      | e 0.00097656 |               | Mask Alarms<br>PAPA alarm |            | Enable Path<br>Step size<br>Length | Path A Path B 0  32 191 192 194 194 194 194 194 194 194 194 194 194 | Path C Path D<br>0 *<br>32 *<br>8191 *<br>0 * | SIF SYNC Inactive<br>Check PAP<br>Mask Alarms<br>PAPA alarm<br>PAPB alarm<br>PAPC alarm |         |

Figure 12. Graphic User Interface of PAP Block in DAC38RF8x Devices

References

| <b>Table 2. Description</b> | of GUI Controls/Indicators | of PAP block |

|-----------------------------|----------------------------|--------------|

|-----------------------------|----------------------------|--------------|

| CONTROL/INDICATORS | FUNCTION                                                                                                                   |

|--------------------|----------------------------------------------------------------------------------------------------------------------------|

| Enable Path        | Enables the power amplifier protection (PAP) logic                                                                         |

| Step size          | Gain attenuation step size for the PAP logic                                                                               |

| Length             | Controls the moving average length                                                                                         |

| Threshold          | Threshold used to trigger PAP logic                                                                                        |

| Wait               | # of clock cycles to wait between ATTENUATE and GAIN states                                                                |

| Sync Source        | used to sync the PAP logic                                                                                                 |

| SIF SYNC           | used to trigger a sync event when SIF SYNC is selected as the SYNC SOURCE                                                  |

| Active             | Indicates when the PAP logic is triggered.                                                                                 |

|                    | ACTIVE = bright green, INACTIVE = dull green                                                                               |

| Check PAP          | Used to read back the current state of the PAP logic.                                                                      |

|                    | If PAP logic is triggered, the Active LED will turn bright green and cannot be reset to dull green by clicking on this LED |

|                    | Note: If PAP logic is not triggered, ACTIVE LED can be toggled between bright and dull green by clicking on the LED        |

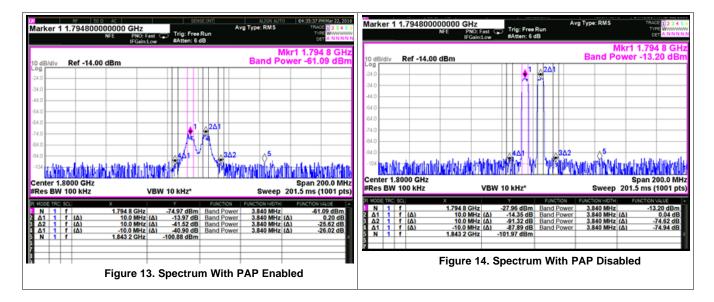

For a 2 x 20 MHz LTE signal centered at 1.79 GHz, the output spectra with and without the PAP in DAC38RF8x enabled is shown in Figure 12. When the PAP is enabled, threshold = 256, Length = 64 and step size = 1/1024.

#### 5 References

1) AN-1433 Base Station Closed-Loop RF Power Control with LMV232 Crest-Fac, Application report, ŚNWA003.

#### 6 **Trademarks**

All trademarks are the property of their respective owners.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated